高速信號采集與數據形成系統硬件設計

根據設計要求,兩片ADC的復位信號同樣需要滿足時序的同步要求。復位信號由FPGA產生以后,FPGA輸出的復位信號分別送入兩片AD芯片的DCLK_RST端,對兩片ADC進行同步復位。

(4)控制信號

該AD轉換器的控制接口有兩種,一種是通過電平控制,另一種可以通過SPI口的復雜控制,通過復雜控制可以在擴展模式下使用該款AD的所有功能。

4 AD與FPGA的數據接口電路

單片ADC的輸出位寬為32Bit,32位并行輸m數據采用一片Vertix5 FPGA接收,并進行串并轉換,對高速采樣數據進行降速、緩存。

Vertex-5是Xilinx推出的Vertex系列的第五代產品,它有24個RocketlO收發器,工作在100Mbps到3.2Gbps之間,內建PCI Express模塊和三重模式以太網媒體訪問控制器(MAC)模塊,支持LVDS,LVPECL等多種信號接口。

每片ADC輸出信號包括32Bit采樣輸出數據、一路數據同步時鐘(DCLK),一路采樣溢出信號(OR),和一路自檢驗進行中的指示信號(CalRun),以上各信號除了CalRun輸出電平均為LVDS。

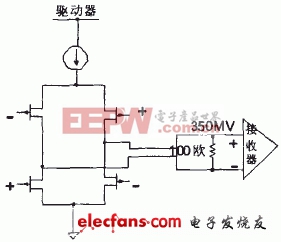

圖4 LVDS工作原理

LVDS(Low Voltage Differential)是一種小振幅差分信號標準。LVDS的典型工作原理如圖一所示,最基本的LVDS器件就是LVDS驅動器和接收器。LVDS的驅動器由驅動差分線的電流源組成,電流通常為3.5mA。LVDS接受其具有很高的輸人電阻,因此驅動器輸出的大部分電流都流過100的匹配電阻,并在接受器的輸入端產生大約350mV的電壓,當驅動器翻轉時,它改變流經電阻的電流方向,因此產生有效的邏輯1和邏輯0狀態。LVDS具有高速、超低功耗、低噪聲和低成本的優良特性。

LVDS在板級設計中應注意以下幾點:(1)盡量保持差分線的等間距與等長,防止引起信號間的相位差而導致的輻射,兩條差分線之間的距離應盡可能近,使接收器的共模抑制能力增強。(2)保持LVDS信號線的PCB電線返回路徑的連續。不要跨越分割,否則跨越分割部分的傳輸線會因為缺少參考平面或參考平面的不連續而導致阻抗的不連續。(3)盡量避免過多的打孔,在滿足流過電流的前提下,孔徑越小,所產生的容性感性越小。(4)避免使用導致阻抗不連續的90度拐角走線,應采用圓弧或135度折線來代替。(5)使用終端電阻實現對差分線的最大匹配,匹配電阻起到吸收負載反射信號的作用,差分阻抗一般控制在85~115之間。

5 FPGA的RocketlO收發器接口的設計

Vertex5的RocketIO收發器采用第四代千兆位級收發器技術,傳輸速度在100Mbps到3.75Gbp之問。在3.75Gbps下每個通道的功率均低于100mW,是業內最低的功耗。采用了先進的TX/RX均衡技術,便于在一些通道上調節收發器,以便實現可靠的操作。內置式的PRBS收發器和檢驗器簡化了特征說明和調試。

本系統使用Vertex5的RocketlO收發器實現了采樣數據的串行輸出。為了保證RocketlO收發器能可靠地工作,硬件電路設計需要遵循一定的要求,需要考慮到以下幾個方面。

(1)參考時鐘設計:

RocketlO收發器需要高精度的差分時鐘,本系統采用Xilinx推薦的高頻低抖動的Epson EG-2121CA差分輸出(LVDS)晶陣.可提供53.125-700MHZ的頻率范圍和低的抖動(RMS Period:3ps; Peak to Peak:25ps).可以滿足設計中RocketlO模塊對參考時鐘性能的要求。

(2)電源設計:

RocketlO收發器的電源引腳對噪聲的影響比較敏感.所以需要進行專門的供電,隔離外圍噪聲源的影響。每一個供電引腳有自己的LC濾波網絡。

(3)PCB設計:

在布線時應特別注意,由于傳輸信號的頻率很高,所以差分信號線在長度上要盡量匹配,嚴重的失配會產生嚴重的抖動和不可預知的時序問題。

6 結束語

本文詳細介紹了一種基于高速轉換芯片ADC08D1500和高端的FPGA Vertex-5的采集系統的設汁,此采集系統的速度達到了1.5G,可以應用在現代寬帶通信中。該系統具有體積小,功耗低,使用靈活方便等特點。特別是RocketlO收發器的應用,極大的提高了芯片之間信號傳輸的速度和可靠性,對于提高雷達的整體性能起到了很大的作用。

文章創新點:基于Vertex5和ADC08D1500的信號采樣與數據形成系統,使用Vertex5的RocketlO收發器采用第四代千兆位級收發器技術使用實現了采樣數據的串行輸出。

模擬信號相關文章:什么是模擬信號

評論