高速信號采集與數據形成系統硬件設計

1 引言

本文引用地址:http://www.104case.com/article/193839.htm雷達回波信號工作在很寬的頻帶上,在對回波信號進行采樣時,根據奈奎斯特采樣定理,采樣頻率必須大于等于被采樣信號最高頻率的兩倍,才能使采樣后的信號不失真。這就使得采樣電路丁作在很高的頻率上,對電路的精度和靠高性提出了很高的要求。本文介紹了的一種高頻高可靠的信號采集和數據形成系統,采樣電路的最高頻率可以達到。

由于FPGA芯片具有體積小,功耗低,開發周期短,配置靈活等優點,本系統以FPGA芯片為核心構筑信號采集和數據形成電路。

2 設計方案

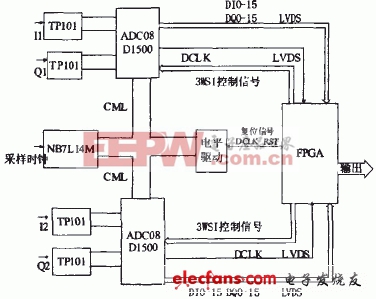

信號采集與數據形成模塊中,采用兩片ADC08D1500同時完成對HH及HV兩個雷達回波通道的正交基帶視頻信號的采樣。使用V5系列FPGA-Vertex5實現對ADC輸出數據的接收,并對接收數據緩存,由FPGA完成數據接口和數據格式化的工作,系統框圖如圖1所示。

圖1數據采集器的整體設計框圖

兩片ADC08D1500對雷達回波的兩個正交通道的基帶視頻信號進行采樣后,采樣數據采用LVDS電平標準輸出,每片ADC輸出位寬為32bit數字信號,采用并行輸出,并由同一片Vertex5 FPGA接收。

FPGA還要實現接口轉換和控制功能,其設置的外部輔助數據接口,接收來自主控的外部輔助數據,外部輔助數據包含了主控計算機對信號采集與數據形成模塊的控制命令。FPGA還設置了兩路32bit位寬的數據記錄接口,將來自兩片ADC的采樣數據與輔助數據一起打包成幀后,通過兩路數據記錄接口或RockeIO接口輸出給數據記錄器。

兩個正交通道的ADC對通道間的工作時序同步有著很高的要求,本方案設計中采用高速時鐘驅動器NB7L14M對采樣時鐘進行驅動,確保到達兩路ADC的采樣時鐘信號的相位一致性。本設計具有自檢功能,可以通過遙測信號將自檢結果傳給主控。此系統以最高頻率1.5G進行設計。

3 AD外圍電路設計

信號采集與數據形成模塊的模數轉換芯片采用ADC08D1500完成,該芯片是National Semiconductor公司推出的一款雙路低功耗CMOS模擬/數字轉換器,取樣頻率為1.7GSPS.分辨率為8Bit,可選擇SDR或者DDR輸出時鐘,采用雙邊采樣(DES)模式,能以3GSPS的速度利用一條模擬輸入通道進行采樣,本系統利用兩條輸入通道以1.5GSPS的速度進行采樣。

(1)模擬輸入

每片ADC08D1500有兩路模擬輸入,分別為VINI和VINQ,輸入模擬數據必須為差分輸入,前端提供的數據源為單端的,采用差分輸入需要采用變壓器將單端信號轉化為差分信號。本設計中的單端模擬輸入信號采用射頻變壓器TP-101,將單端信號轉換為差分信號后接入ADC的模擬信號輸人端。

(2)時鐘輸入

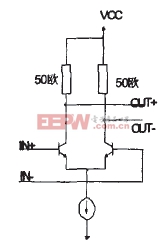

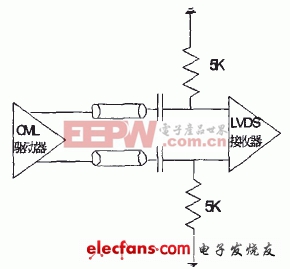

ADCOSDl500芯片有一個LVDS的差分時鐘輸入端CLK+和CLK-。為交流耦合差分輸入。輸入的時鐘信號通過一個4.7nF的電容耦合到ADC的時鐘輸入端。根據設計要求,兩片ADC的采樣時鐘需受嚴格同步,以達到其幅相一致性的要求。驅動器設計中采用了一片on semiconductor公司的1:4高速時鐘分配芯片NB7L14M完成。該芯片的輸入信號電平為LVPECL、CML、LVDS、LVTTL和LVCMOS,輸出信號為標準的CML電平,交流耦合到ADC的時鐘輸入端。CML電平的輸出結構如下圖所示。CML接口典型的輸出電路是一個差分對形式,差分對的發射極到地的恒流源典型值為16mA。假定CML的輸出負載為一個50上拉電阻,則單端CML輸出信號的擺幅為Vcc口Vcc-0.4V。在這種情況下,差分輸出信號擺幅為800mv。CML到LVDS的交流耦合電路圖如下圖。

圖2 CML輸出機構

圖3 CML到LVDS在交流耦合電路圖

模擬信號相關文章:什么是模擬信號

評論