正余弦編碼器細(xì)分技術(shù)研究

4 電路原理圖

用6片比較器LM339和5片異或門7486來搭建電路,實(shí)驗(yàn)用的電路板如圖11所示。

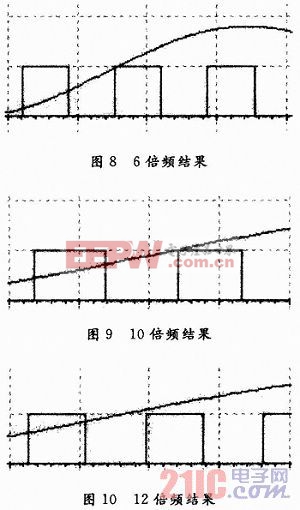

該電路結(jié)構(gòu)簡(jiǎn)單,成本低,易于實(shí)現(xiàn)。由結(jié)果分析可知,隨著倍頻倍數(shù)的增加,比較器的滯后性越發(fā)明顯,因此不能為了追求高倍頻而無限制地使用比較器。

5 結(jié)論

用該硬件細(xì)分方法實(shí)現(xiàn)的信號(hào)細(xì)分,電路結(jié)構(gòu)簡(jiǎn)單,成本低,讀數(shù)迅速,能達(dá)到動(dòng)態(tài)測(cè)量的要求。雖然隨著倍頻倍數(shù)的增加,比較器的滯后性會(huì)越明顯,但是在低倍頻時(shí),還是一種比較好的方案,在提高正余弦編碼器方面比較實(shí)用,該方法通過仿真調(diào)試和實(shí)驗(yàn),驗(yàn)證了該方案是可行的。

比較器相關(guān)文章:比較器工作原理

評(píng)論