基于CPCI和光纖接口的數據采集卡設計與實現

摘要:設計了一套基于CPCI總線,PCI9054橋接芯片和可編程邏輯器件(FPGA)的高速數據采集卡。FPGA作為本地主控芯片,根據工控機經PCI9054轉發(fā)的采集命令,通過光纖接口實現與雷達接收機的通信。采用高速RAM緩存數據,采集的接收機測試數據的分析結果可在工控機上顯示,從而實現了對雷達接收機性能的快速測試。該采集卡具有較強的通用性和可擴展性,詳細介紹了高速數據采集卡的組成和工作原理、硬件設計。

關鍵詞:光纖接口;CPCI總線;PCI9054;FPGA;雷達接收機測試

隨著雷達技術的發(fā)展和雷達型號的增多,現代雷達接收機數據處理速度顯著提高。因此,在雷達接收機的測試和維護中,對接收機測試系統(tǒng)的數據處理能力、可擴展性等性能要求也在不斷提高。傳統(tǒng)的雷達接收機測試系統(tǒng)由于專用性強、兼容性差、擴展能力不足,而CPCI總線的通用性、高可靠性和抗震動性使其在雷達信號處理板中得到廣泛的應用。同時,由于傳輸高速雷達信號的需求,光纖在雷達系統(tǒng)中得到了廣泛的應用。基于以上分析,本文設計并實現了一種基于光纖接口,使用CPCI總線通信的高速、通用性強的高速數據采集卡。通過實際測試,該采集卡可以很好地完成數據采集等雷達接收機測試的功能,并具有較好的通用性和可擴展性。

1 系統(tǒng)設計

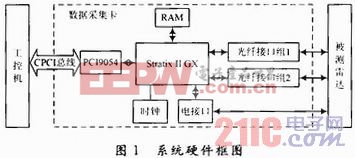

高速數據采集卡主要由StratixⅡGX FPGA、光纖接口、SRAM、PCI9054橋接芯片等構成。本系統(tǒng)設計的目的是應用于雷達數據的采集和分析,為了高速、可靠地傳輸雷達信號,決定采用光纖作為傳輸媒介,充分利用光纖傳輸損耗小、抗干擾能力強、傳輸速率高等優(yōu)點。

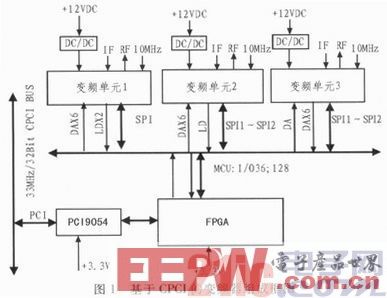

采用FPGA作為信號采集系統(tǒng)的核心,這種方式最大的優(yōu)點就是結構靈活,有較強的通用性,適合模塊化設計,能夠提高效率,同時其開發(fā)周期較短,系統(tǒng)容易維護和擴展。圖1是該系統(tǒng)的硬件框圖。

其工作流程如下:PC機通過CPCI接口將采集命令等送入FPGA,FPGA對命令進行譯碼,通過光纖接口向雷達接收機發(fā)出參數設置命令,然后通過光纖接口接收采集的雷達接收機數據。光纖接口將光信號轉換成串行電信號送入FPGA,FPGA對數據進行串/并轉換、數據緩沖等所必須的信號處理過程,然后存儲到高速RAM中。當計算機發(fā)出數據傳輸命令后,再將數據通過CPCI總線送入計算機進行存儲、分析處理和顯示等。同時系統(tǒng)還保留了一部分電信號的接口,便于和現有的系統(tǒng)兼容。

2 系統(tǒng)硬件設計

2.1 時鐘設計

系統(tǒng)中FPGA的時鐘信號由一個125 MHz晶振直接提供,PCI9054的時鐘由一個40 MHz晶振提供。高速RAM和光纖接口的時鐘信號則是由FPGA通過內部的PLL提供。因為時鐘信號是非常敏感的信號,所以要盡量減少反射和串擾等一些問題。在時鐘信號線上串接適當的匹配電阻可以有效地減少反射,減少串擾則需要在時鐘走線周圍留出額外的空間。在本設計中,將時鐘線單獨放在兩個地平面層中間的一層,保證了時鐘信號的完整性。

2.2 CPCI接口設計

目前,PCI接口的設計有兩種方法,一種為使用專用的PCI接口芯片來設計,這種方法相對來說較為簡單;另一種方法是利用FPGA進行設計,這種方法比較復雜,開發(fā)難度較大。本設計采用第一種方法,即采用PCI9054接口芯片實現PCI總線。

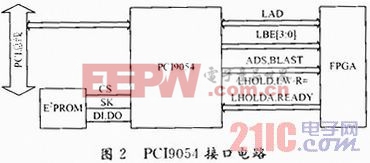

PCI9054芯片適用于通用的32位、33 MHz的局部總線設計。它的本地總線可為三種模式:M模式,C模式和J模式,可利用模式選擇引腳加以選擇。本設計選用C模式,即32位的地址/數據總線非復用。

PCI9054提供了三種物理總線接口:PCI總線接口、LOCAL總線接口、串行EPROM接口。CPCI接口設計思路是:FPGA通過PCI9054與PCI總線相連,在FPGA內部實現PCI本地端的時序控制。PCI9054芯片內部2個獨立DMA通道,可以實現系統(tǒng)數據在PC機內存與數據采集卡之間的高速傳輸。PCI9054接口電路如圖2所示。

評論