基于LabVIEW的FPGA模塊FIFO深度設定實現

本文引用地址:http://www.104case.com/article/193640.htm

4 數據連續傳輸的LabVIEW實現

在本文中系統軟件包括兩部分:Host vi和FPGAvi,二者是獨立而又有聯系的兩個部分。Host vi運行于主控計算機上,FPGA vi運行于FPGA上,二者通過FIFO來傳輸數據。

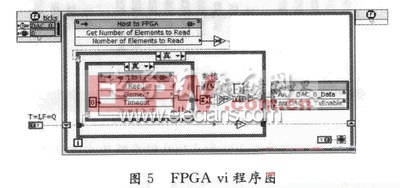

4.1 FPGA程序設計

使用圖形化的編程環境LabVIEW FPGA模塊來定義FPGA邏輯,除了具有上述的優點以外,LabVIEW作為一種并行結構的編程語言,非常適用于FPGA的并行結構,能夠十分方便地實現多線程并行任務。

當FPGA vi開始運行時,從Host vi讀取數據的FIFO需要一定的初始化時間,時間長度與FIFO的深度成正比。在初始化期間FIFO輸出一系列的無效默認值。為了不讓無效值進入到下一級的運算中,在DMA方式的FIFO之前加了一個FIFO函數——Get Number of Element to Read,該函數用于獲得FIFO內有效數據的數量。當有效數據的數量大于0時,再開始進行下一級運算。考慮到FPGA有限的硬件資源和FPGA FIFO最小值的限制,將數據的地址寬度設為M=11,根據上文分析DMA FIFO的深度設為2M+5=2 053 KB。

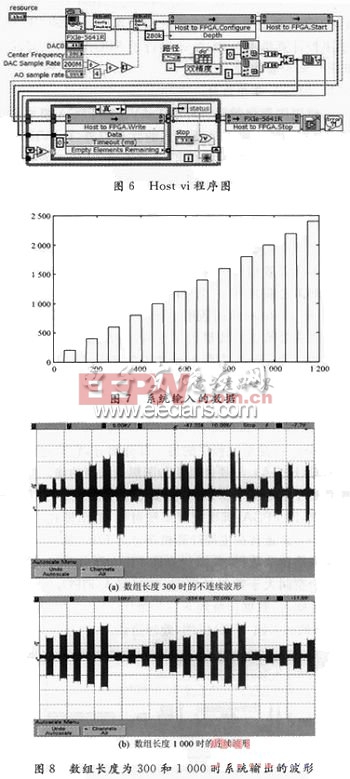

4.2 主控計算機程序設計

Host vi是系統程序的另一部分部分,它具有建立硬件對象(FPGA)、與硬件通信和圖形顯示等功能。主控計算機程序圖如圖6所示,首先要建立與之進行通信的硬件對象,即FPGA;其次配置系統時鐘、輸出模式;再次創建FIFO,設置其在主控計算機部分的FIFO深度;然后從電子表格讀取數據,并循環查詢FIFO剩余空間的大小,當剩余空間大于數組長度時,數據寫入FIFO當沒有足夠的空間時,數據保留到下一個循環,滿足條件后再寫入FIFO;最后關閉FIFO應用,處理錯誤。

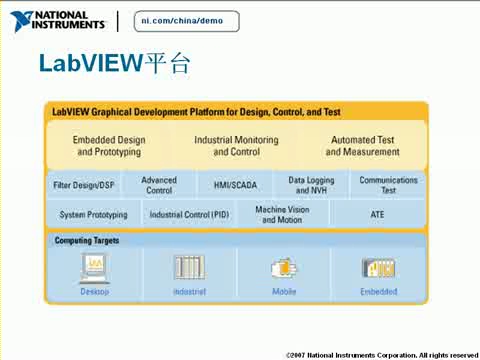

當輸入數組長度分別為300和1 000,形狀如圖7所示的波形時,輸出數據的波形如圖8所示。由于AD9857上變頻的原因,使得輸出波形在輸入的矩形包絡中帶有載波,載波頻率為60 MHz。根據表1中的數據可以得出結論:此處的編程和上述實驗的結果是一致的,即FPGA輸出頻率為10 MHz,數組長度大于500時,系統數據的輸出是連續。同時此結果也表明本文中的LabVIEW程序實現了數據的連續傳輸。

5 結語

通過設定合適的FIFO深度,實現了數據的連續傳輸,為后續的工程設計奠定了基礎。該設定FIFO深度的方法也對其他使用LabVIEW FPGA模塊的工程設計具有一定的參考價值。

評論