基于諧波混頻的微波低相噪鎖相設計

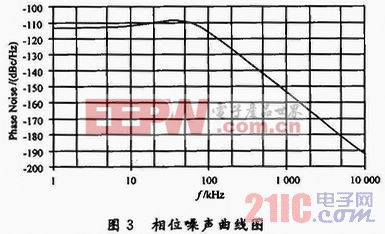

環路濾波器的輸入端連接著ADF4113集成鑒相器,輸出端連接著壓控振蕩器VCO。濾波器具有低通特性,可以起到低通濾波器的作用,但更重要的是它還對環路參數的調整起著決定性的作用,從而對環路性能產生重要影響。該設計采用四階RC積分濾波器,如圖3所示。本文引用地址:http://www.104case.com/article/193521.htm

四階RC積分濾波器的各部分作用如下:C1建立濾波;R2,C2建立鎖相;R3,C3優化濾波;R4,C4進一步優化濾波。環路濾波器具體參數設計在此不再贅述。

2 系統指標仿真與測試

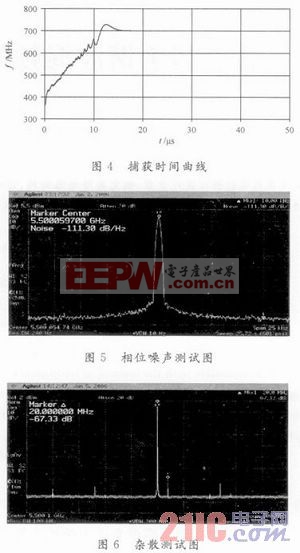

采用AD公司提供的鎖相環仿真軟件ADI SimPLL,在輸入頻率為700 MHz,環路帶寬為200 kHz時得到了環路相位噪聲曲線和捕獲時間曲線如圖3,圖4所示,可見相位噪聲能夠滿足小于-110 dBc/Hz@10 kHz的要求,且環路能夠在20μs內鎖定。

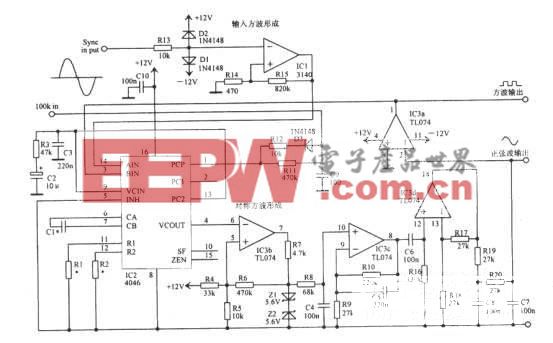

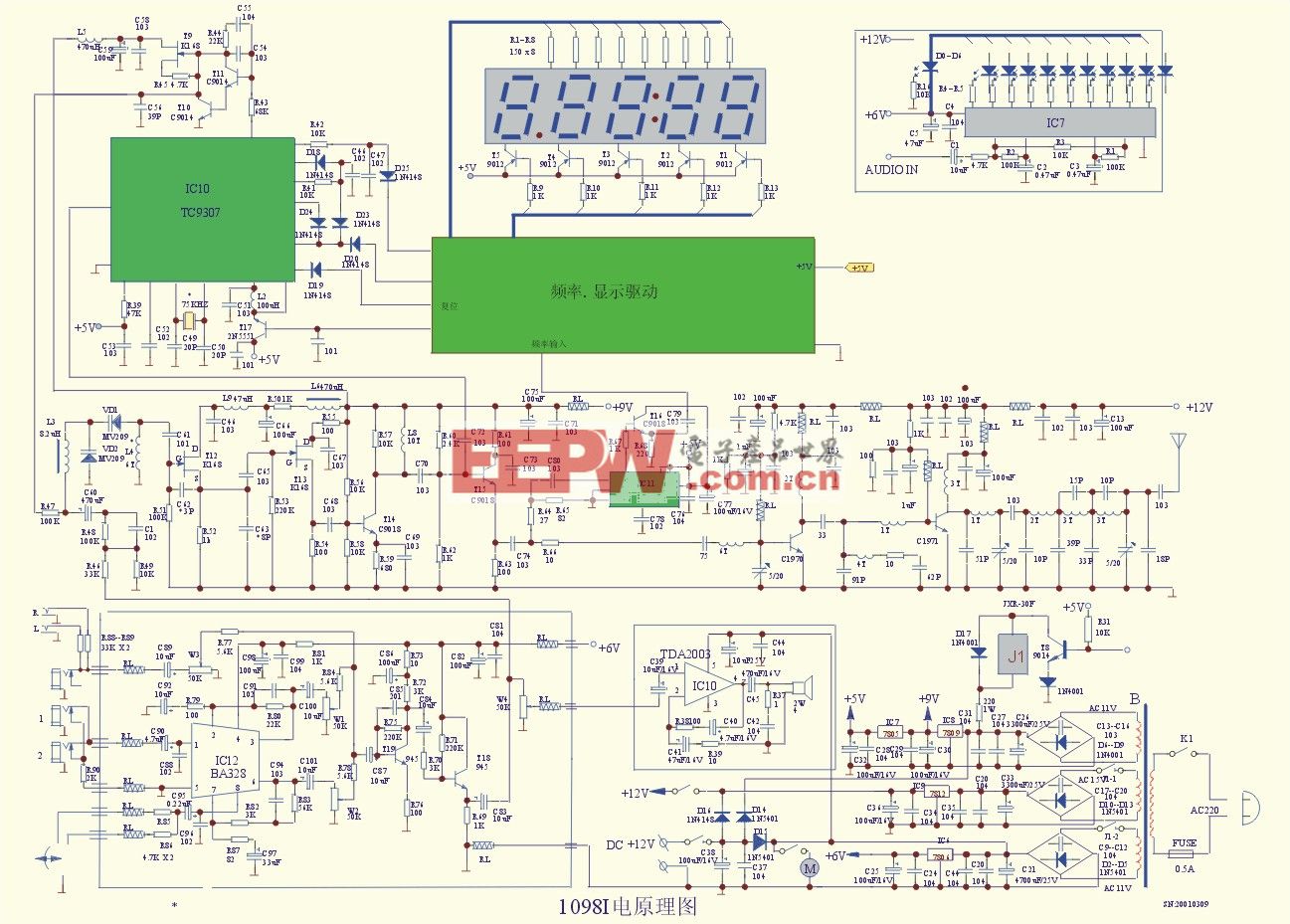

最終本電路的測試圖如圖5,圖6所示。由圖5,圖6可見相位噪聲及雜散都能滿足預期指標要求。

3 結語

該設計利用諧波混頻實現了預期的全部主要指標,輸出頻率為5.5 GHz;輸出功率為0.5 dBm;相位噪聲達到-111.30 dBc/Hz@10 kHz;雜散抑制達到-67.33 dBc。該電路的雜散水平還可以通過合理走線得到的設置屏蔽盒等措施提高,并且混頻工作部分只使用了高通濾波器,導致許多諧波信號也混雜在鑒相器的射頻輸入端而沒有被濾除,如果使用5.5 GHz的帶通濾波器效果會更好。

評論