基于諧波混頻的微波低相噪鎖相設計

摘要:該設計通過諧波混頻的方式實現常規分頻式鎖相環所難以實現的低相噪指標。在理論分析的基礎之上,提出微波低相噪鎖相環設計方案,制定實際電路結構,通過對電路的調試達到在5.5 GHz頻點輸出-111.30 dBc/Hz@10 kHz的相噪指標和-67.33 dBc的雜散指標。驗證了通過諧波混頻的方式實現微波低相噪鎖相的可行性。

關鍵詞:低相噪;諧波混頻;鎖相源;雜散指標

0 引言

眾所周知鎖相環的環路帶寬以內的相位噪聲主要由晶體振蕩器經過倍頻惡化后的相位噪聲與鑒相器引入的相位噪聲共同決定。對于環路帶寬以外的相位噪聲則主要由VCO的相位噪聲和鑒相器引入的噪聲基底惡化共同決定。也即是PLL對參考晶體噪聲源呈現低通特性,而對VCO噪聲呈現高通特性。因此通過常規的分頻鎖相方式,由于鑒相器鑒相頻率較高以及噪聲基底的惡化無法取得較好的相噪指標。

本振相位噪聲水平很高的時候,射頻輸出的相位噪聲與混頻后中頻信號的相位噪聲基本上一致,這就提供了一種獲得低相噪的解決方式,即通過諧波混頻的方式降低鑒相器射頻輸入端的頻率,并采用相噪水平很好的本振,基底噪聲不會進一步惡化,這樣系統輸出的相位噪聲由鑒相器的相位噪聲決定。由于將鑒相器的射頻反饋輸入頻率大大降低,使輸出信號的相位噪聲較之常規的分頻式鎖相環得以很大程度上的改善。

1 鎖相源電路設計

1.1 電路指標

本次微波低相噪鎖相設計的預期技術指標有:

(1)相位噪聲:-110 dBc/Hz@10 kHz。

(2)工作頻率:5.5 GHz。

(3)雜散水平:小于-60 dBc。

(4)輸出功率:大于0 dBm。

1.2 電路設計

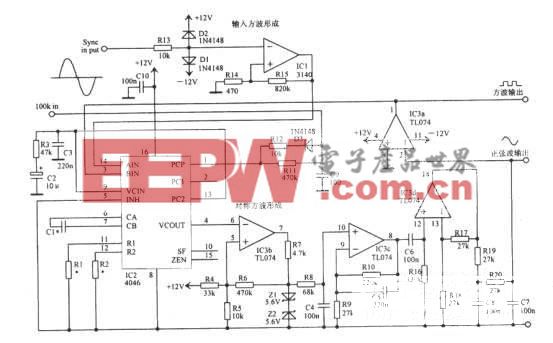

鎖相環的基本組成是由VCO,鑒相器,低通濾波器,參考頻率源等所組成。該設計所采用諧波混頻與常規的分頻式鎖相系統不同,諧波混頻鎖相系統在反饋回路中并未采用一般的分頻器而是采用諧波混頻來對反饋的振蕩信號進行處理在反饋給鑒相器的射頻輸入端口。這樣做的目的在于使系統可以通過混頻的方式取得相噪水平較好的中頻信號反饋給鑒相器的射頻反饋輸入端實現鎖相系統輸出的低相噪的信號,這是分頻式鎖相系統難以達到的指標。其原理框圖如圖1所示。

該電路中鑒相器采用美國模擬器件公司的ADF4113,環路濾波器由RC積分濾波器構成,VCO的工作頻率在5.5 GHz,這里采用Hittite公司的HMC431LP4。在設計中,預留了一個輸入和一個輸出端口,其中一個作為VCO的反饋信號送給諧波混頻工作部分的輸出端口,其輸出端口的信號頻率為5.5 GHz;另一個端口作為鑒相器反饋輸入信號端口。5.5 GHz的射頻信號在諧波混頻工作部分中與本振為1.2 GHz的射頻輸入信號的四次諧波混頻,最后輸出700 MHz的中頻信號反饋給鑒相器鑒相,從而得到控制電壓控制VCO的輸出信號頻率,實現諧波混頻鎖相的功能。

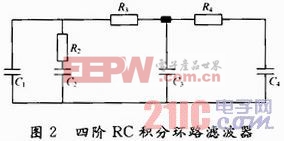

環路濾波器的輸入端連接著ADF4113集成鑒相器,輸出端連接著壓控振蕩器VCO。濾波器具有低通特性,可以起到低通濾波器的作用,但更重要的是它還對環路參數的調整起著決定性的作用,從而對環路性能產生重要影響。本設計采用四階RC積分濾波器,如圖2所示。

評論