通用電路板自動測試系統(tǒng)方案設(shè)計與實現(xiàn)

2.3 數(shù)據(jù)傳輸和控制協(xié)議本文引用地址:http://www.104case.com/article/193505.htm

系統(tǒng)中待測信號較多,低頻和高頻部分分別是32 個,而數(shù)據(jù)采集芯片都只有一個,各個信號都是由FPGA 控制模擬開關(guān)分時地進(jìn)行采集的。為使各個通道的數(shù)據(jù)存儲、傳輸和控制有序地進(jìn)行,在FPGA 中為每一個信號都設(shè)置了工作狀態(tài)控制模塊和數(shù)據(jù)存儲模塊(以下稱為寄存器和數(shù)據(jù)存儲器)。本系統(tǒng)中所有控制過程的命令都是從PC 端發(fā)出的,F(xiàn)PGA 接收控制指令后,按指令進(jìn)行相應(yīng)的操作。

(1)寄存器和數(shù)據(jù)存儲器介紹。FPGA 對每一路信號都設(shè)有5 bit 的控制寄存器、12 bit 的最終結(jié)果寄存器和16 bit 的原始數(shù)據(jù)存儲器。此外在高頻部分還擁有一個公共的高速采樣數(shù)據(jù)的存儲器,大小為1 kB,及其對應(yīng)的一個8 bit 的控制寄存器。5 bit的控制寄存器每個通道只設(shè)有一個,該寄存器D3 位為數(shù)據(jù)準(zhǔn)備好標(biāo)志(1 有效),其余4 位為控制位,各位的功能見表1,每一位都是1 為肯定,每一位都可通過PC 端發(fā)來的控制指令更改,F(xiàn)PGA 只能向D3 位寫1 ,表示數(shù)據(jù)已經(jīng)準(zhǔn)備好。上電或復(fù)位后該寄存器值為33333B。

表1 5bit控制寄存器的位功能

12 bit 的最終結(jié)果寄存器每個通道也只設(shè)有一個,該寄存器的值是向PC 機(jī)發(fā)送的最終結(jié)果。該寄存器的數(shù)據(jù)在低頻和高頻部分,存放的數(shù)據(jù)不同:低頻部分存放的是13 次采樣結(jié)果的平均值,高頻部分存放的是計算后的頻率值。

16 bit 的原始數(shù)據(jù)存儲器,其低頻和高頻部分的數(shù)量是不相同的:高頻部分一般是2 個,分別用來存放標(biāo)準(zhǔn)和待測時鐘的計數(shù)值;低頻部分為13 個,用來存放13 個采樣點的值,12 bit 的最終結(jié)果寄存器的值是根據(jù)這13 個數(shù)據(jù)的平均值。

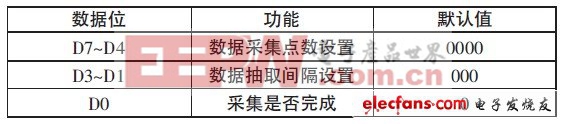

高速采樣數(shù)據(jù)存儲器是高頻部分的32 路共有的,由于波形采樣的數(shù)據(jù)量比較大,本系統(tǒng)設(shè)計時在同一時刻只允許采樣1 路信號,采樣點數(shù)可以設(shè)定(最多為1 K),待這些數(shù)據(jù)全部發(fā)送出后,才可以開始下一次采集。對應(yīng)的控制寄存器的位功能見表2。

表2 高速采樣控制寄存器的位功能

其中D7~D4 為數(shù)據(jù)采集的點數(shù)設(shè)置,3333B 表示64 個,1111 表示1 324 個,步進(jìn)為64。D3~D1 為數(shù)據(jù)抽取的間隔設(shè)置,333 表示抽取間隔為3,全部數(shù)據(jù)有效;111 表示抽取間隔為28,即每隔28 個點抽取一個點,步進(jìn)為4。設(shè)置這幾位的目的是為了適應(yīng)信號頻率的要求,防止采集數(shù)據(jù)不足一周期的狀況發(fā)生。D3位為標(biāo)志位,功能和操作與5 bit 的寄存器的對應(yīng)位完全相同。本寄存器分高4 位和低4 位兩次設(shè)置。

(2)控制命令介紹。本系統(tǒng)中的控制命令都是由PC 機(jī)發(fā)出的,共8 個命令:選擇控制寄存器1(低頻部分);選擇控制寄存器2(高頻部分);選擇控制寄存器3(高速采樣部分);寫控制寄存器數(shù)據(jù);讀取數(shù)據(jù)1(低頻部分);讀取數(shù)據(jù)2(高頻部分的頻率值);讀取波形采樣數(shù)據(jù);開始/停止測試。

PC 機(jī)發(fā)送的控制字都是8 位的,其中高3 位為控制命令字,用來區(qū)分8 個命令,低5 位為輔助功能,具體見表3。FPGA 接收到主機(jī)發(fā)來的命令信號后,按命令執(zhí)行相應(yīng)的操作。

表3 控制命令的位功能

(3) 數(shù)據(jù)傳輸過程簡述。系統(tǒng)中與PC 機(jī)的通信采用的是RS232 接口,數(shù)據(jù)的傳輸完全符合RS232 標(biāo)準(zhǔn)。現(xiàn)將數(shù)據(jù)的傳輸過程簡述如下:系統(tǒng)啟動后,首先進(jìn)行自檢,以確定系統(tǒng)工作是否正常;系統(tǒng)工作正常后,PC 機(jī)通過測試軟件對FPGA 內(nèi)部的各個寄存器進(jìn)行配置;然后發(fā)送開始命令,開始對有效的各個信號進(jìn)行采集;采集完成后向PC 機(jī)返回信息,PC 機(jī)根據(jù)需要通過測試軟件從FPGA 讀取相應(yīng)通道的數(shù)據(jù),將數(shù)據(jù)計算后與標(biāo)準(zhǔn)值進(jìn)行比較并得出測試結(jié)果。也可以根據(jù)需要讀取某一通道的原始數(shù)據(jù)以及采集某一通道信號的波形。在FPGA 內(nèi)部還擁有關(guān)鍵信號(電源)的監(jiān)測:任何一路電源信號不正常則重新進(jìn)行采集,若3 次采集結(jié)果均不正常則直接關(guān)閉電路板的供電電源,避免損壞電路板,并向PC 發(fā)送電源不正常的消息,并給出出現(xiàn)異常的通道號。

2.4 測試軟件設(shè)計

測試軟件是本系統(tǒng)的人機(jī)接口部分,在本系統(tǒng)中需包括如下功能:設(shè)置各個通道信號的參數(shù)值,并能保存和讀取設(shè)置的參數(shù);顯示各個通道的信號測試結(jié)果,并能夠保存;能夠采集并顯示某一通道的信號波形。

擁有上述功能即可進(jìn)行測試,至于界面方面可以根據(jù)個人的習(xí)慣和愛好進(jìn)行設(shè)計。本系統(tǒng)的測試軟件實現(xiàn)了上述的功能,至于界面并未追求美觀,其功能大致如下:

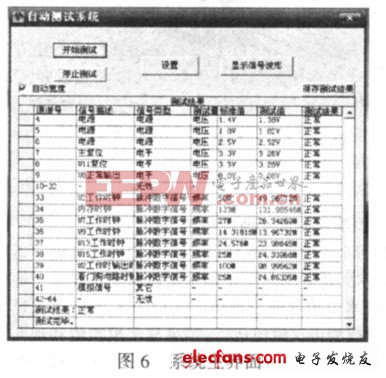

系統(tǒng)主界面見圖6,除了“開始停止”鍵外,有設(shè)置、查看信號波形和保存結(jié)果3 個按鈕,還有一個結(jié)果的輸出窗口。

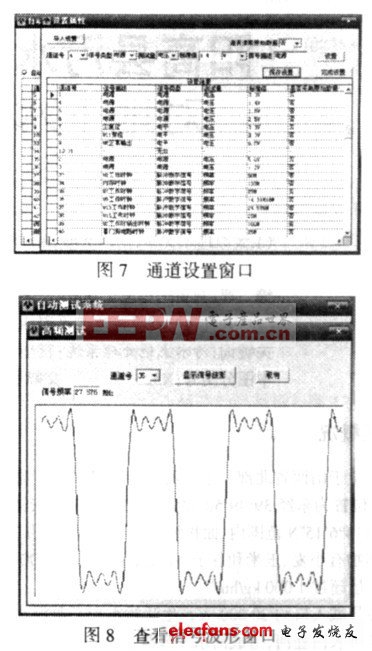

設(shè)置窗口見圖7,本窗口中可以設(shè)置每一路信號的屬性,也可以直接調(diào)出以前保存的設(shè)置,設(shè)置完成后即可按該設(shè)置進(jìn)行測試。設(shè)置完成后,可以將本次的設(shè)置保存成文件,以便下次直接調(diào)出。

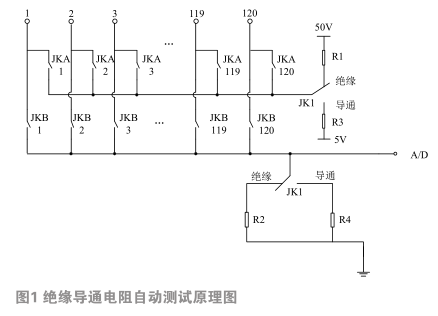

查看信號波形的設(shè)置和顯示窗口見圖8。

3 結(jié)語

本文設(shè)計的電路板自動測試系統(tǒng)通用性強(qiáng)、使用方便、工作穩(wěn)定,可以應(yīng)用于多款電路板的測試;對不同的電路板,只需制作2 塊對應(yīng)的固定板即可。系統(tǒng)已經(jīng)對123 mm×133 mm 和253mm×213 mm 兩款電路板進(jìn)行測試,結(jié)果令人滿意。該系統(tǒng)具有一定的推廣價值。

評論