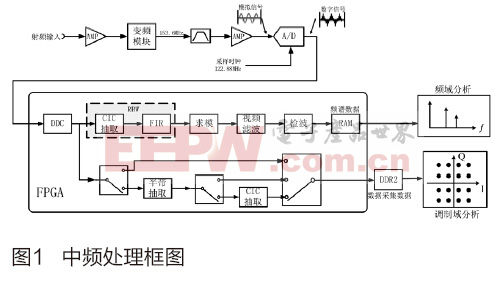

一種短波軟件無線電臺數(shù)字中頻單元的設(shè)計(jì)與實(shí)現(xiàn)

3 系統(tǒng)測試

3.1 測試方法

3.1.1 DDC測試方法

信號源輸出頻率為501 kHz.幅度為100μV,12.3μV的正弦波到本系統(tǒng)的中頻信號輸入端,本系統(tǒng)的音頻信號輸出端接至綜測儀進(jìn)行測試。測試結(jié)果如圖6所示。本文引用地址:http://www.104case.com/article/193237.htm

3.1.2 DUC測試方法

信號源輸出頻率為1 kHz,幅度為100μV的正弦波到本系統(tǒng)的音頻信號輸入端,本系統(tǒng)的中頻信號輸出端接至頻譜儀進(jìn)行測試。測試結(jié)果如圖7所示。

上述實(shí)現(xiàn)方案用于實(shí)際電臺中,通過大量的室內(nèi)測試和室外遠(yuǎn)距離測試,通話效果良好,實(shí)測性能指標(biāo)達(dá)到國內(nèi)領(lǐng)先水平。并且由于采用了純數(shù)字的中頻處理技術(shù),使電臺的成本控制、可靠性、可維護(hù)性、整機(jī)的體積和功耗,以及功能的可擴(kuò)充性都得到極大的改善。

3.2 測試結(jié)果分析

圖6(a)在100μV信號輸入幅度下,音頻在600 Ω,輸出2.45 V的情況下音頻失真度1%;圖6(b)在滿足SINAD=12 dB的時(shí)候,中頻信號輸入幅度為12.3 μV即可,完全滿足接收系統(tǒng)要求(系統(tǒng)要求中頻信號輸入幅度為50μV要滿足SINAD=12 dB)。

由圖7(a)可見,在近端(10 kHz)滿足信噪比大于等于50 dB。近端無雜散;由圖7(b)可見,在遠(yuǎn)端(200 kHz)雜散抑制大于等于70 dB。

5 結(jié)語

本文設(shè)計(jì)了一種短波民用電臺的中頻數(shù)字處理單元及基于FPGA的實(shí)現(xiàn)方法,同時(shí)也對音頻信號的處理流程做出分析研究。由于FPGA在設(shè)計(jì)和修改上的靈活性,使其比ASIC更加適合實(shí)現(xiàn)數(shù)字上下變頻及多模式調(diào)制解調(diào)功能。本文方案測試結(jié)果性能良好,已在實(shí)際軟件無線電電臺中得到應(yīng)用,具有推廣應(yīng)用價(jià)值。

評論