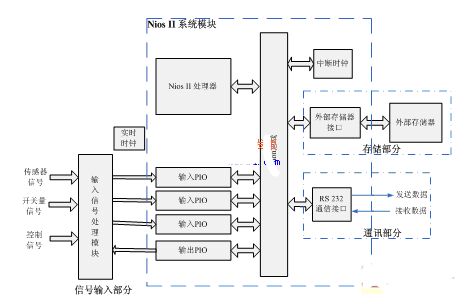

基于Nios軟核處理器的溫備份智能容錯系統設計方案

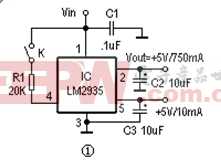

6)SDRAM控制器,用于連接片外64MB同步動態隨機訪問存儲器,以便于為程序提供運行環境。

7)UART0和UART1通過電平轉換芯片(MAX3232)轉換成RS-232電平以便與服務器通過串口通信。

8)WD Timer定時器,在這里作為看門狗定時器使用,以便提高仲裁器的可靠性,在仲裁器中運行的程序出現故障時,它給系統提供復位信號。

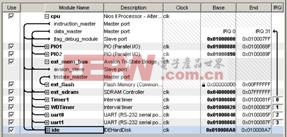

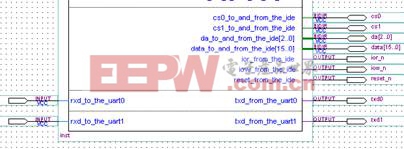

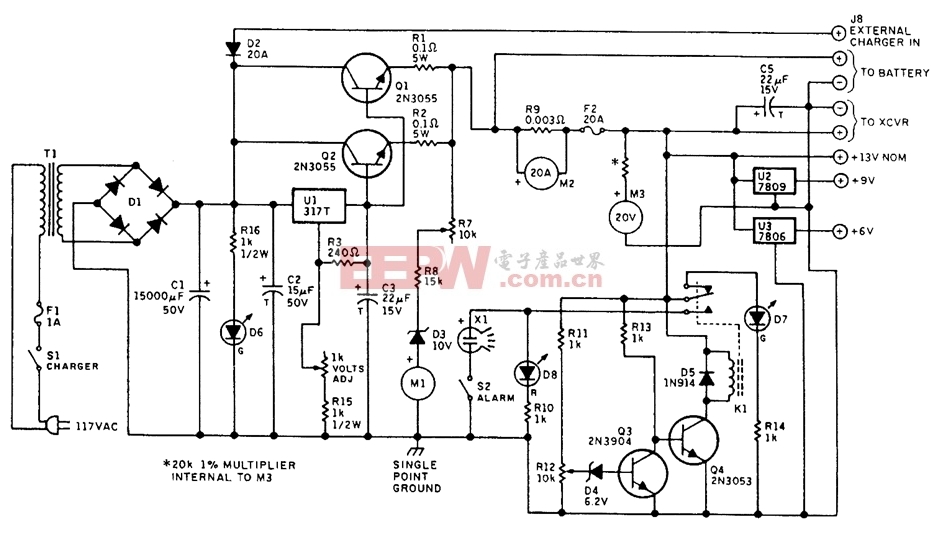

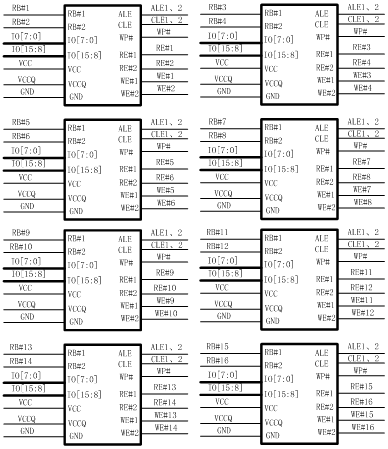

該系統是使用Quartus II進行硬件設計的,用其中的SOPC Builder工具[4]進行Avalon架構設計,圖3是仲裁器的Avalon架構的設計最終界面。由于篇幅有限,此處僅提供UART0、UART1和IDE硬盤相關的部分原理圖,如圖4所示。

圖3 SOPC Builder設計界面

圖4 部分原理圖

4.2 軟件設計思想

以上主要介紹了硬件部分的設計思想,下面簡單描述一下軟件開發的相關思想。該仲裁器的軟件開發使用Nios IDE[6](Nios集成開發環境),主要包括如下模塊:

1)狀態獲取模塊:該模塊被Timer1定時器中斷例程定期調用,主要用于獲取服務器的當前狀態,其設計流程如圖5所示:

圖5 狀態獲取模塊流程

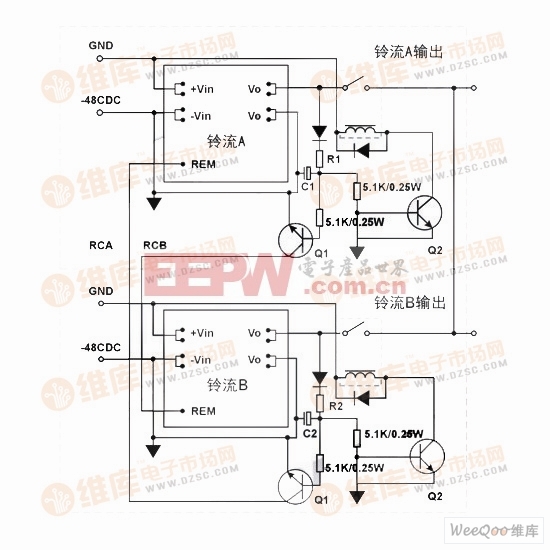

2)顯示模塊:用于輸出用戶關心的信息,如根據服務器的狀態用不同顏色點亮雙色發光二極管、顯示當前時間間隔等級以及控制蜂鳴器報警。

3)通訊模塊:主要用于與服務器進行通訊,以便給服務器發送命令以及獲得工作服務器的同步信息并把同步信息寫入硬盤中。

4)按鍵處理模塊:用于處理用戶按鍵,根據不同的按鍵進行不同的控制,如:開/關繼電器以及設置時間間隔等級。

5)硬盤訪問模塊:用于提供對硬盤進行讀寫操作的函數,以便需要操作硬盤的模塊調用。

6)讀寫Flash的模塊:用于讀取/修改仲裁器的相關參數,如:各服務器運行時間,檢測服務器狀態的時間間隔等。

5 結 論

本文提出的軟硬件設計思想經實踐證明是可行的,并且在實際的系統中工作良好。該思想可以進一步推廣到多機容錯系統中。在多機系統中,我們在定制好各臺機器的工作計劃后,就可以利用本文提到的給每臺服務器一個計劃運行時間這一思想來解決實際問題。另外,使用Nios軟核處理器,可以定制很多的UART口,這一點就遠遠優于需要擴展串口電路的普通單片機,從而在硬件設計和軟件設計上大大降低了難度。

本文作者創新點:1) 采用SOC(系統級芯片)設計出溫備份高速仲裁器。2) 將同步信息放到了仲裁器中。這樣,所有同步信息就不依賴于工作設備(如PC機),所以即使工作設備出現故障也無妨,這樣就大大提高了系統的可靠性。3) 能夠對工作設備進行計劃定制,傳統的溫備份仲裁器沒有這一功能。

參考文獻

[1] 王仲生.智能故障診斷與容錯控制[M].西安:西北工業大學出版社,2005。

[2] 潘松,黃繼業,曾毓.SOPC技術實用教程[M].北京:清華大學出版社,2005。

[3] 宋保維,系統可靠性設計與分析.西安:西北工業大學出版社,2000。

[4] Sylvain Poussier, Hassan Rabah, Serge Weber.SOPC-based Embedded Smart Strain Gage Sensor. Lecture Notes in Computer Science[J],2002,2438:1131-1132。

[5] 徐光輝,程東旭等.基于FPGA的嵌入式開發與應用[M].北京:電子工業出版社,2006。

[6] 郭書軍,王玉花, 葛紉秋.嵌入式處理器原理及應用——Nios系統設計和C語言編程[M].北京:清華大學出版社,2004。

[7] 沙占友,孟志永,王彥朋.單片機外圍電路設計(第2版)[M].北京:電子工業出版社,2006。

[8] 王俊卿,楊揚,劉慶文.基于NIOS軟核處理器的uClinux的移植[J].微計算機信息,2005,21-1:123-124。

評論