淺談FPGA設計原則與技巧

前言

本文引用地址:http://www.104case.com/article/193067.htmFPGA(Field-Programmable Gate Array),即現場可編程門陣列,作為專用集成電路領域中的一種半定制電路,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展下的產物。近幾年來由于FPGA器件的應用十分廣泛,而FPGA設計是使用FPGA器件必不可少的一部分,所以了解與掌握有關FPGA設計知識是十分必要的。

FPGA設計的基本原則及常用模塊

基本原則:一 面積和速度的平衡與互換;二硬件原則;三 系統原則;四 同步設計原則;

常用模塊:一 RAM;二 FIFO;三 全局時鐘資源與時鐘鎖相環;四 全局復位、置位信號

四種常用FPGA設計思想與技巧

FPGA設計思想與技巧是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA設計工作種取得事半功倍的效果。常用的FPGA設計思想與技巧,包括乒乓球操作、串并轉換、流水線操作和數據接口的同步方法。

FPGA設計思想之一乒乓操作

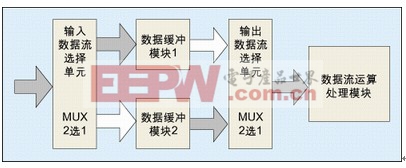

“乒乓操作”是一個常常應用于數據流控制的處理技巧,典型的乒乓操作方法如圖1所示。

乒乓操作的處理流程為:輸入數據流通過“輸入數據選擇單元”將數據流等時分配到兩個數據緩沖區,數據緩沖模塊可以為任何存儲模塊,比較常用的存儲單元為雙口RAM(DPRAM)、單口RAM(SPRAM)、FIFO等。在第一個緩沖周期,將輸入的數據流緩存到“數據緩沖模塊1”;在第2個緩沖周期,通過“輸入數據選擇單元”的切換,將輸入的數據流緩存到“數據緩沖模塊2”,同時將“數據緩沖模塊1”緩存的第1個周期數據通過“輸入數據選擇單元”的選擇,送到“數據流運算處理模塊”進行運算處理;在第3個緩沖周期通過“輸入數據選擇單元”的再次切換,將輸入的數據流緩存到“數據緩沖模塊1”,同時將“數據緩沖模塊2”緩存的第2個周期的數據通過“輸入數據選擇單元”切換,送到“數據流運算處理模塊”進行運算處理。如此循環。

圖2:采用雙口RAM,并在DPRAM后引入一級數據預處理模塊實現用低速模塊處理高速數據流。

另外,巧妙運用乒乓操作還可以達到用低速模塊處理高速數據流的效果。如圖2所示,數據緩沖模塊采用了雙口RAM,并在DPRAM后引入了一級數據預處理模塊,這個數據預處理可以根據需要的各種數據運算,比如在WCDMA設計中,對輸入數據流的解擴、解擾、去旋轉等。假設端口A的輸入數據流的速率為100Mbps,乒乓操作的緩沖周期是10ms。

通過乒乓操作實現低速模塊處理高速數據的實質是:通過DPRAM這種緩存單元實現了數據流的串并轉換,并行用“數據預處理模塊1”和“數據預處理模塊2”處理分流的數據,是面積與速度互換原則的體現!

串并轉換設計技巧

串并轉換是FPGA設計的一個重要技巧,它是數據流處理的常用手段,也是面積與速度互換思想的直接體現。FPGA設計思想中的串并轉換的實現方法多種多樣,根據數據的排序和數量的要求,可以選用寄存器、RAM等實現。前面在乒乓操作的圖例中,就是通過DPRAM實現了數據流的串并轉換,而且由于使用了DPRAM,數據的緩沖區可以開得很大,對于數量比較小的設計可以采用寄存器完成串并轉換。如無特殊需求,應該用同步時序設計完成串并之間的轉換。比如數據從串行到并行,數據排列順序是高位在前,可以用下面的編碼實現:

prl_temp={prl_temp,srl_in};

其中,prl_temp是并行輸出緩存寄存器,srl_in是串行數據輸入。

對于排列順序有規定的串并轉換,可以用case語句判斷實現。對于復雜的串并轉換,還可以用狀態機實現。

流水線操作設計思想

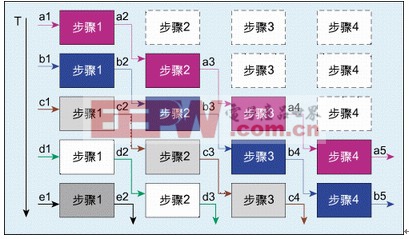

圖3:流水線設計的結構示意圖

流水線設計的一個關鍵在于整個設計時序的合理安排,要求每個操作步驟的劃分合理。如果前級操作時間恰好等于后級的操作時間,設計最為簡單,前級的輸出直接匯入后級的輸入即可;如果前級操作時間大于后級的操作時間,則需要對前級的輸出數據適當緩存才能匯入到后級輸入端;如果前級操作時間恰好小于后級的操作時間,則必須通過復制邏輯,將數據流分流,或者在前級對數據采用存儲、后處理方式,否則會造成后級數據溢出。

在WCDMA設計中經常使用到流水線處理的方法,如RAKE接收機、搜索器、前導捕獲等。流水線處理方式之所以頻率較高,是因為復制了處理模塊,它是面積換取速度思想的又一種具體體現。

圖4:流水線設計時序示意圖

數據接口的同步方法

數據接口的同步是FPGA設計的一個常見問題,也是一個重點和難點,很多設計不穩定都是源于數據接口的同步有問題。

在電路圖設計階段,一些工程師手工加入BUFT或者非門調整數據延遲,從而保證本級模塊的時鐘對上級模塊數據的建立、保持時間要求。還有一些工程師為了有穩定的采樣,生成了很多相差90度的時鐘信號,時而用正沿打一下數據,時而用負沿打一下數據,用以調整數據的采樣位置。這兩種做法都十分不可取,因為一旦芯片更新換代或者移植到其它芯片組的芯片上,采樣實現必須從新設計。而且,這兩種做法造成電路實現的余量不夠,一旦外界條件變換(比如溫度升高),采樣時序就有可能完全紊亂,造成電路癱瘓。

總結

由于FPGA既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點,可以快速成品,也可以被修改來改正程序中的錯誤和更便宜的造價。所以電子工程師們開發設計是在普通的FPGA上完成然后將設計轉移到一個類似于ASIC的芯片上。本文主要介紹了FPGA設計的基本原則和FPGA設計的思想與技巧。

評論