基于DSP和FPGA的汽車防撞高速數(shù)據(jù)采集系統(tǒng)

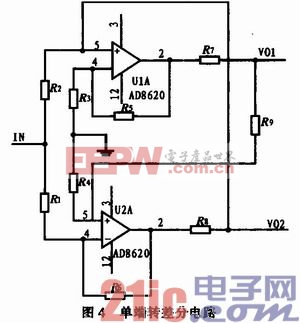

2.1.2 前端差分電路

為了消除偶次諧波分量,抑制共模噪聲源,起到系統(tǒng)抗干擾的效果,本系統(tǒng)的AD轉(zhuǎn)換電路采用差分輸入的形式,而信號經(jīng)過放大電路后得到的是單端信號,所以,必須要將前端的輸入單端信號轉(zhuǎn)化為差分信號。本設(shè)計選用了ADI公司生產(chǎn)的AD8620驅(qū)動芯片構(gòu)成差分驅(qū)動電路,其具體電路設(shè)計如圖4所示。本文引用地址:http://www.104case.com/article/192881.htm

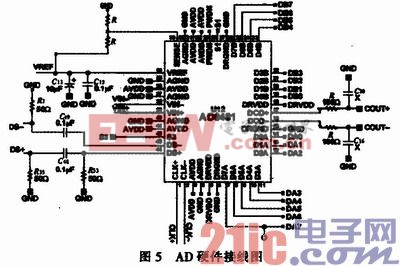

2.2 AD轉(zhuǎn)化電路

在數(shù)據(jù)采集系統(tǒng)中AD是比較重要的環(huán)節(jié),主要完成對激光回波信號的采集工作,而采樣時鐘信號可以由FPGA電路內(nèi)部的時鐘模塊來提供。ADI公司的AD9481,可以采用差分輸入,采樣率達(dá)到250 MSPS,并且采用250 M的PECL標(biāo)準(zhǔn)的時鐘信號,為此在設(shè)計中為產(chǎn)生該差分時鐘信號,考慮選用MC100LEL16的時鐘芯片。AD9481的數(shù)字輸出屬于并行接口,有16位的數(shù)據(jù)流,對于這么高速的數(shù)據(jù)與存儲會出現(xiàn)競爭冒險,使系統(tǒng)不穩(wěn)定,因此在設(shè)計時AD與FPGA的輸出端之間串接了一個100 Ω的電阻,可以消除出現(xiàn)在0~1之間的毛刺與高速數(shù)據(jù)線之間的干擾,具體的AD硬件原理如圖5所示。

2.3 數(shù)據(jù)處理部分硬件電路

本系統(tǒng)數(shù)據(jù)處理部分由FPGA和DSP兩個部分來完成。根據(jù)前一級AD電路的信號輸出時序進(jìn)行VHDL編程,來實現(xiàn)同時對兩路AD輸出的數(shù)字信號的采集,將數(shù)據(jù)輸入到FIFO模塊中,然后通過EMIF總線將數(shù)據(jù)快速傳輸?shù)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/DSP">DSP里進(jìn)行相關(guān)算法的運算。

2.3.1 FPGA電路

FPGA采用硬件編程實現(xiàn)復(fù)雜的邏輯功能,不僅能夠?qū)Σ杉降拇笈繑?shù)據(jù)流進(jìn)行預(yù)處理,而且作為整個控制系統(tǒng)的核心部分,提供系統(tǒng)所需的時鐘信號,保證數(shù)據(jù)的有序采集,而且作為數(shù)據(jù)傳輸?shù)募~帶,保證了AD與DSP進(jìn)行數(shù)據(jù)傳輸。結(jié)合采樣存儲傳輸?shù)裙δ蹻PGA的模塊主要分為4個部分:時鐘管理模塊、A/D控制模塊、FIFO緩存模塊、與DSP的EMIF接口模塊:

1)時鐘管理模塊,該部分主要是產(chǎn)生系統(tǒng)所需的各模塊的時鐘信號,本系統(tǒng)采用ISE軟件自帶的DCM模塊來實現(xiàn)。

2)A/D控制器:根據(jù)當(dāng)前選擇的采樣模式為A/D提供相應(yīng)的控制信號以使A/D正常工作;并通過AD電路的信號輸出時序?qū)D輸出的數(shù)字信號進(jìn)行采集。

3)FIFO緩存模塊:主要實現(xiàn)將高速采集到的數(shù)據(jù)緩存到FIFO中。當(dāng)緩存滿時,F(xiàn)IFO的滿標(biāo)志(full)向DSP申請中斷,DSP相應(yīng)中斷后采用DMA傳輸方式把采樣效據(jù)讀到內(nèi)存中進(jìn)行數(shù)據(jù)實時處理。

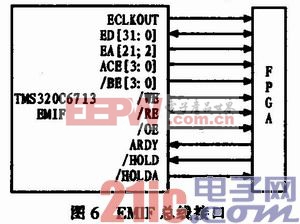

4)與DSP的EMIF接口模塊:DSP通過EMIF接口與FPGA內(nèi)部的RAM連接,實現(xiàn)了將FPGA中緩存的數(shù)據(jù)與DSP進(jìn)行高速傳輸?shù)淖饔谩?br />2.3.2 DSP與FPGA的接口設(shè)計

本系統(tǒng)在設(shè)計中DSP主要是通過C6713器件的外部存儲器接口EMIF與FPGA進(jìn)行數(shù)據(jù)通信。外部存儲器接口(EMIF)是TMS DSP器件上的一種接口。一般來說,EMIF可實現(xiàn)DSP與不同類型存儲器(SRAM、Flash RAM、DDR-RAM等)的連接。用EMIF與FPGA相連,從而使FPGA平臺充當(dāng)一個協(xié)同處理器、高速數(shù)據(jù)處理器或高速數(shù)據(jù)傳輸接口。

其EMIF的總線接口圖如圖6所示。

評論