基于過零點檢測的高分辨率DAC靜態測試方法研究

圖中,虛線表示標準參考信號f(t)=Asin(ωt+φ),實線為疊加之后的信號,可以看出,tk1、tk2、tk3時刻為過零點,Vk的大小由△tk決定。△tk的值可以通過測量過零點tk1、tk2、tk3得到,Vk的表達式可以推導如下:

其中,Nc為在時間間隔△tk內的采樣點數,fs為設置的ADC的采樣率。

1.3 測試方法的弊端

利用以上方法,可以得到DAC輸出電壓的值Vk,進而求出靜態參數DNL、INL的大小。需要關注的是:為了得到過零點序列,參考正弦波的幅值A必須大于DAC的滿量程電壓范圍;同樣由式(5)得到ADC的最低采樣率:

△V幅值分辨率,通過式(6)可以看出:為了確保測試的準確性,△V應該盡可能地小,并且在其他條件不變的情況下Nc的值越大越好。因為這種方法的本質在于將幅度上的高精度測試轉移到時間上來。因此采樣率越高,測量結果越準確,但是采樣率與測試設備息息相關,不可能無限制提高。這種情況下,如果沒有設備能夠提供足夠高的采樣率,那么只能降低信號頻率f。但是降低信號頻率f將帶來另一個問題,就是測試時間的成倍增加。

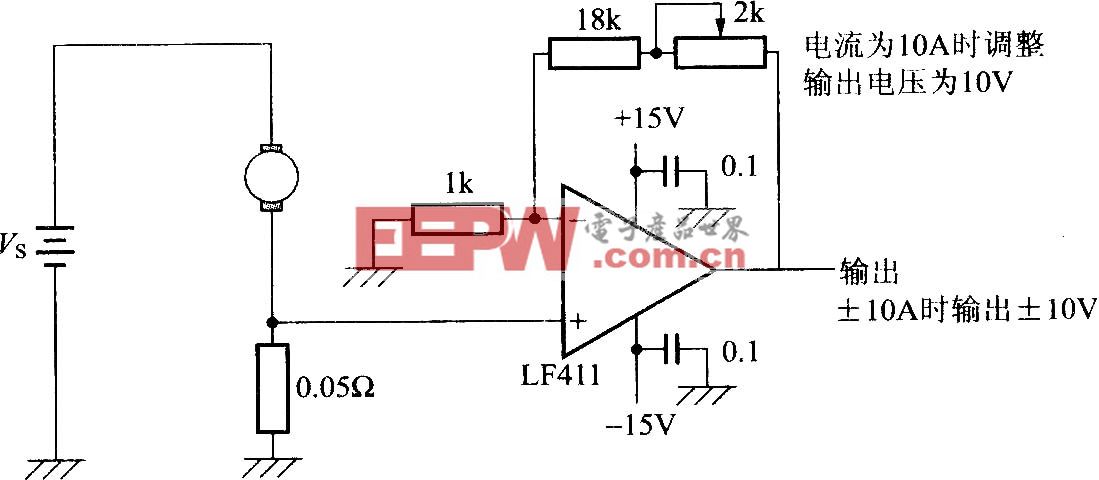

在文獻中作者曾對16位且幅值為±10V的DAC進行了實測,采用泰克TDS7404B數字示波器作為采集信號用的ADC。其主要參數為:8位分辨率、20GS/s的最高采樣率。設置△V=LSB/40,Nc=5,正弦波頻率f=100Hz,幅值A=11V。通過式(6)得到的采樣率高達5GS/s。每次測10個Vk對其做平均,這樣每測一個Vk花費的時間是0.1s,即便擁有這樣的超高采樣率的設備,完整地測一個16位的DAC所需要的時間也至少需要兩個小時。

2 提出的方法

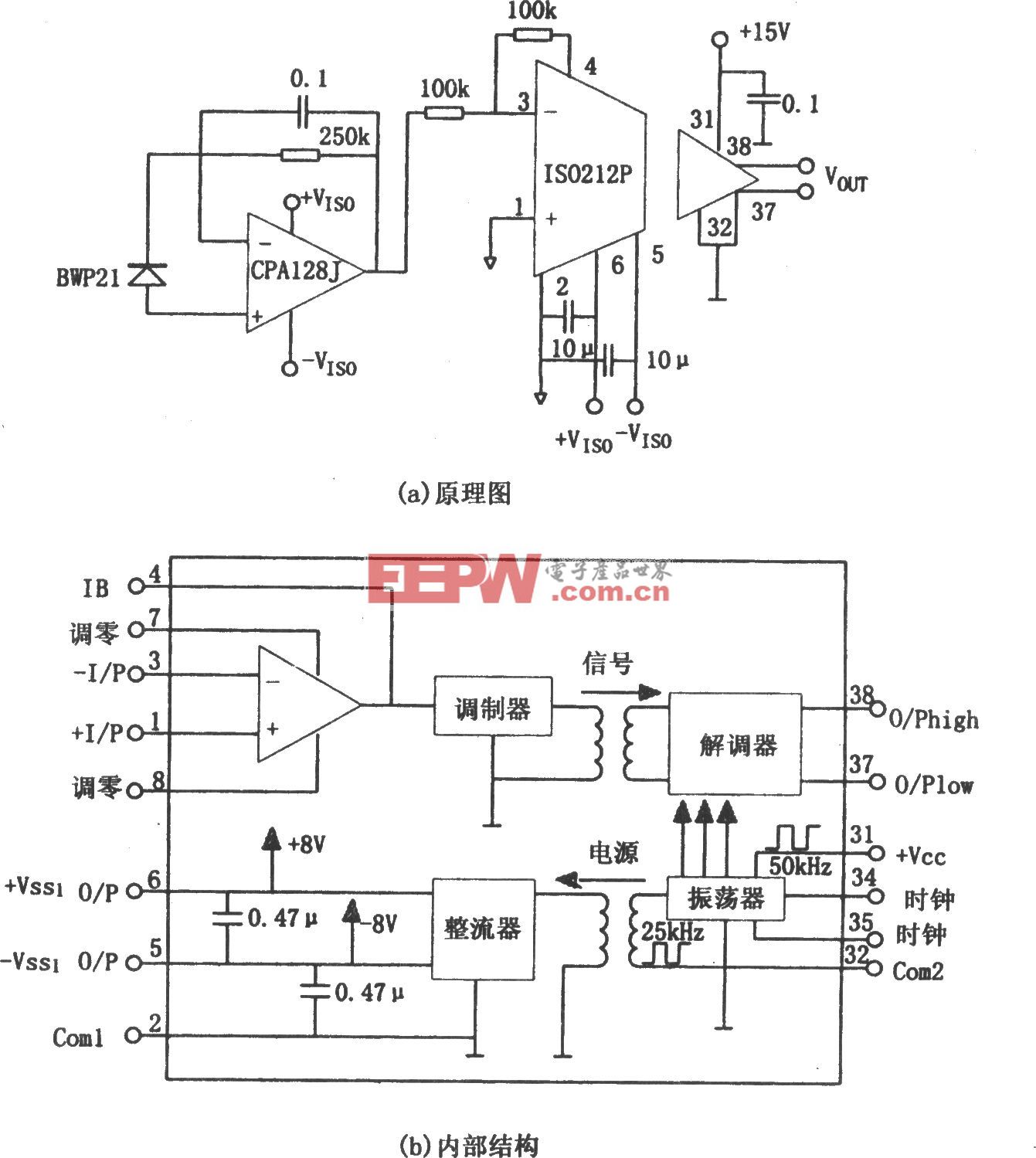

從降低測試時間的角度考慮:首先,從圖3中可以看到,利用正弦波作為參考波形至少需要3個過零點才能得到DAC的輸出電壓值,其次,為了降低檢測每個過零點所需要的時間,最直接的方法就是提高參考信號的頻率f,但是由于設備條件的限制,采樣率fs不能再提高。從式(6)中可以看出,Nc、△V都是約定值,不可變動,唯一能改變的就是參考正弦波幅值A,但A的最小值也受到限制,因為一旦A小于被測DAC的量程范圍,DAC中大于A的輸出電壓將無法測得。實際上,A的限制是因為我們需要測試每一個代碼對應的輸出電壓值。本文引用地址:http://www.104case.com/article/192774.htm

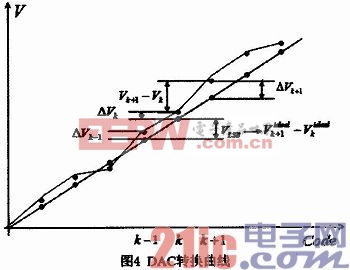

但事實上,我們并不需要測試每一個Vk。對靜態測試而言,主要是了解被測DAC的線性度,如圖4所示。影響DNL的主要是相鄰兩個輸入代碼的輸出電平幅值之差與理想步長之間的偏差,即Vk+1-Vk與LSB之差。將DNL、INL的計算公式適當變化如下:

由圖4和式(7)、(9)可以看出,只要知道輸入代碼的實際電壓與理想電壓的差值,一樣能計算出DAC的靜態參數。

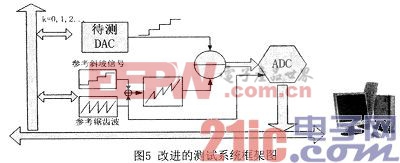

基于以上認識,設計了如下的測試系統架構模型。

評論