基于DDS技術的任意波形發生器研究與設計

1.1 DDS基本原理

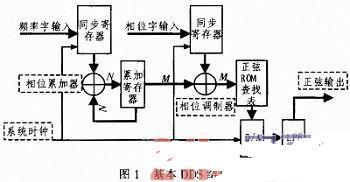

直接數字合成技術(Direet Digital Synthesis,簡稱DDS)是建立在采樣定理基礎上,首先對需要產生的波形進行采樣,將采樣值數字化后存入存儲器作為查找表,然后通過查表讀取數據,再經D/A轉換器轉換為模擬量,將保存的波形重新合成出來。DDS基本原理框圖如圖1所示。

由圖l看出,除了濾波器(LPF)之外,DDS系統都是以數字集成電路實現,因此DDS系統易于集成和小型化。DDS系統的參考時鐘源通常是一個具有高穩定性的晶體振蕩器,整個系統的各個組成部分提供同步時鐘。頻率字(FSW)實際上是相位增量值(二進制編碼),作為相位累加器的累加值。相位累加器在每一個參考時鐘脈沖輸入時,累加一次頻率字,其輸出相應增加一個步長的相位增量。由于相位累加器的輸出連接在波形存儲器(ROM)的地址線上,因此其輸出的改變就相當于查表。這樣就可把存儲在波形存儲器內的波形抽樣值(二進制編碼)經查找表查出。ROM的輸出送到D/A轉換器,經D/A轉換器轉換成模擬量輸出。

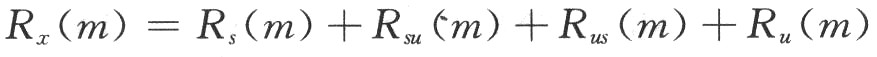

1.2 DDS的基本參數及其計算

在系統時鐘脈沖的作用下,相位累加器不停累加,即不停查表,把波形數據送到D/A轉換器轉換成模擬量輸出,從而合成波形。濾波器則進一步平滑D/A轉換器輸出的近似正弦波的鋸齒階梯波,同時衰減不必要的雜散信號。設頻率字(FSW)的值為d,系統時鐘頻率為f,相位累加器的字長為N,則系統的輸出頻率為:

2 任意波形發生器的設計方案

基于DDS技術的任意波形發生器主要由微處理器控制模塊、鍵盤與顯示模塊、DDS通道的FPGA實現模塊、D/A轉換模塊以及濾波器模塊組成。同時片外擴展了4 KB程序存儲器SRAM和6 KB數據存儲器ROM,分別用于存儲波形抽樣數據和3種標準輸出波形抽樣數據。本系統設計原理如圖2所示。

2.1 微處理器控制模塊

采用AT89C5l單片機完成數據處理和控制其他電路工作。將鍵盤接收的數據通過特定算法轉換成二進制碼,再將處理后的控制字、波形參數和其他器件的控制信號發送出去。

由于AT89C5l單片機主要接口有:微處理器與擴展器件的接口;微處理器與FPGA模塊的接口;微處理器與鍵盤、顯示模塊的接口;微處理器與輸出幅值調節電路的接口。由于單片機的輸出引腳有限,需擴展其引腳。本設計采用8255器件擴展單片機的輸出引腳,8255的PA用于相位控制字的輸出;PB用于頻率控制字的輸出;PC是位可控輸出端,用于DDS工作方式的控制字和波形參數的控制字輸出引腳。AT89C5l單片機與FPGA的接口電路如圖3所示。

2.2 鍵盤與顯示模塊

由于本系統設計的測量裝置需要設置輸出波形、頻率、電壓等參數,而且監控程序需要菜單驅動,因此需要設置鍵盤。鍵盤采用外接44軟鍵盤,使用軟件掃描方式獲得按鍵信息。因為按鍵需要去抖動,因此采用軟件編程方式實現,這樣可以節省硬件資源,簡化電路設計。

液晶顯示可提供人機交互界面和系統運行狀態,選用精工的MGLS 19264液晶顯示屏。該液晶顯示屏內置2塊HD61202U液晶顯示驅動控制器。其中CSA,CSB作為左、右屏片選信號,接單片機A8、A9引腳。同時單片機用地址Al作為R/W信號控制數據總線的數據流向;地址AO作為D/I信號控制寄存器的選擇;E信號由單片機的讀信號RD和寫信號WR合成產生,實現計算機對內置HD61202U圖形液晶顯示模塊的電路連接。電位器用來調節顯示屏的對比度,如圖4所示。液晶顯示左半屏命令字地址為0EOOH;狀態字地址為0EIOH;寫顯示命令字地址為0E0lH;讀顯示命令字地址為0EllH;右半屏對應地址為0D00H、0D10H、0D0lH、0DllH。

2.3 DDS通道的FPGA實現模塊

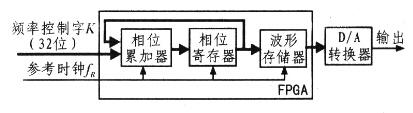

該模塊設計是DDS信號合成的關鍵部分,主要由相位累加器、地址總線控制器、數據總線控制器與SRAM組成。其中,除了SRAM外,其余3個模塊都由FPGA實現。

相位累加器是整個DDS系統的關鍵,直接影響整個系統的功能。圖5給出的FPGA結構框圖中相位累加器實質上是一個帶反饋的29位加法器,它把輸出數據作為反饋數據和由微處理器送來的頻率控制字連續相加,從而產生有規律的29位相位地址碼。設計中采用流水線技術實現29位加法。當輸入所需頻率時,轉換成頻率控制字來驅動FPGA工作,從而產生所需波形頻率。整個模塊設計過程使用FPGA的開發軟件實現并進行仿真。

2.4 D/A轉換模塊

D/A轉換器是DDS系統的核心器件,其速度和特性直接影響整個系統的性能。從建立時間、尖峰脈沖能量、位數和積分線性等四個方面選擇D/A轉換器。因為DDS系統的工作頻率一般都很高,因此首先應選用高速D/A轉換器。其次是考慮信噪比問題,增大D/A轉換器的位數,可減小電壓幅值量化誤差,增大信噪比,因此,采用了12位的D/A轉換器。

2.5 濾波器模塊

濾波器分為兩組:一組是橢圓函數濾波器,用于正弦波的濾波;另一組是線性濾波器,用于其他標準波形的濾波。

3 結語

本系統設計的DDS電路采用FPGA實現,單片機控制整個系統,產生任意波形。因此,基于DDS技術的波形發生器結構簡單,成本低,而且提高了信號源輸出信號的分辨率。使用FPGA設計的DDS電路要比采用專用DDS器件更靈活,性價比更高。但在設計時應注意線路板的布線,以減少外界干擾,降低輸出信號的雜散性。

評論