一種正弦信號發生器的設計

1 引言

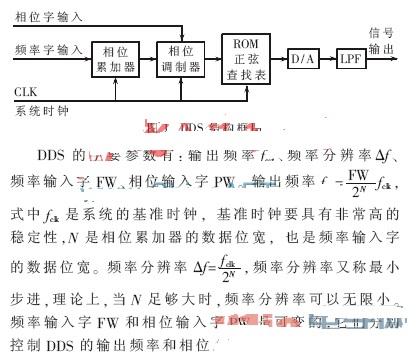

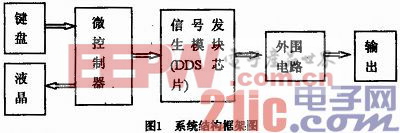

直接數字頻率合成技術(DDS)具有頻率分辨率高,切換速度快,可輸出相位連續、任意的波形信號,能夠實現全數字自動化控制等優點,使其成為雷達,通信等信號源的首選。因此,提出一種基于DDS AD9851的正弦信號發生器,該系統利用FPGA和單片機技術設計,并可根據實際應用需求,現場設置相關信號源參數,操作簡單,界面友好,具有廣泛的應用前景。

2 系統整體設計

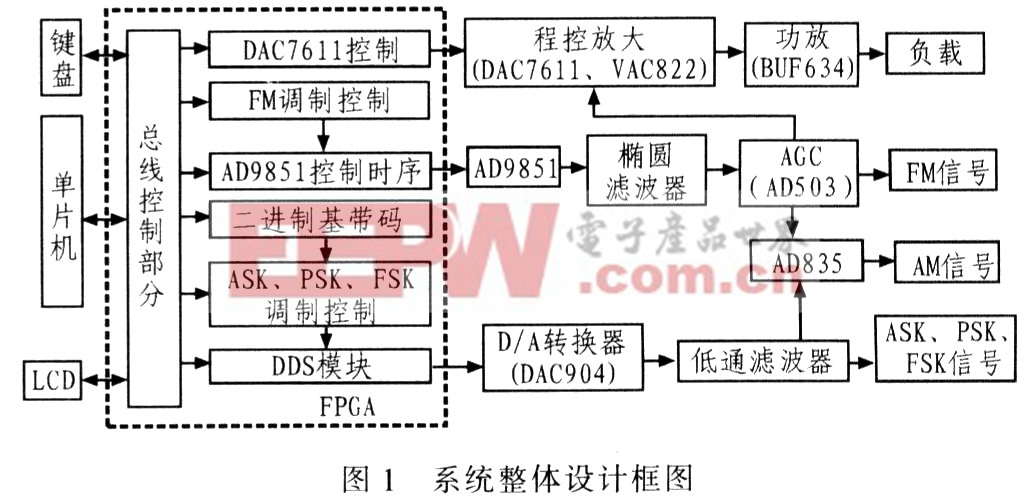

該系統利用AD9851產生正弦信號和幅度調制AM、頻率調制FM的載波信號,FP(認自制 DDS產生二進制振幅鍵控ASK、二進制移相鍵控PSK、二進制移頻鍵控FSK基波信號,模擬乘法器AD835產生AM信號,而利用軟件調制產生FM、 ASK、FSK和PSK信號。單片機控制D/A轉換器所產生的電壓作為DDS輸出信號的基準電壓,調節調制信號。后級采用OPA656和BUF634構成的功率放大電路驅動50 Ω負載。圖1為系統整體設計框圖。

3 硬件電路設計

3.1 AD9851模塊

AD9851是采用先進CMOS技術具有高集成度的直接數字合成器,內置32位頻率累加器、10 bit高速D/A轉換器、高速比較器和可選通的時鐘電路。通過控制內部5個輸入數據寄存器的控制字實現其可編程功能,數據總線D0~D7完成并行工作,由 W_CLK引腳接入的控制字寫時鐘觸發寫入。

具體輸入方式如圖2所示,有效復位信號RESET使輸入數據地址指針指向第1個輸入寄存器,W_CLK上升沿寫入第1組8位數據,指針指向下一個輸入寄存器,連續5個W_CLK上升沿完成全部40位控制數據的輸入,此后W_CLK信號上升沿無效。FQ_UD上升沿到來時這40位控制數據由輸入寄存器寫入頻率/相位控制寄存器,更新輸出頻率和相位,同時把地址指針復位到第1個輸入寄存器,等待下一組新數據的寫入。

評論