圖像采集系統的Camera Link標準接口設計

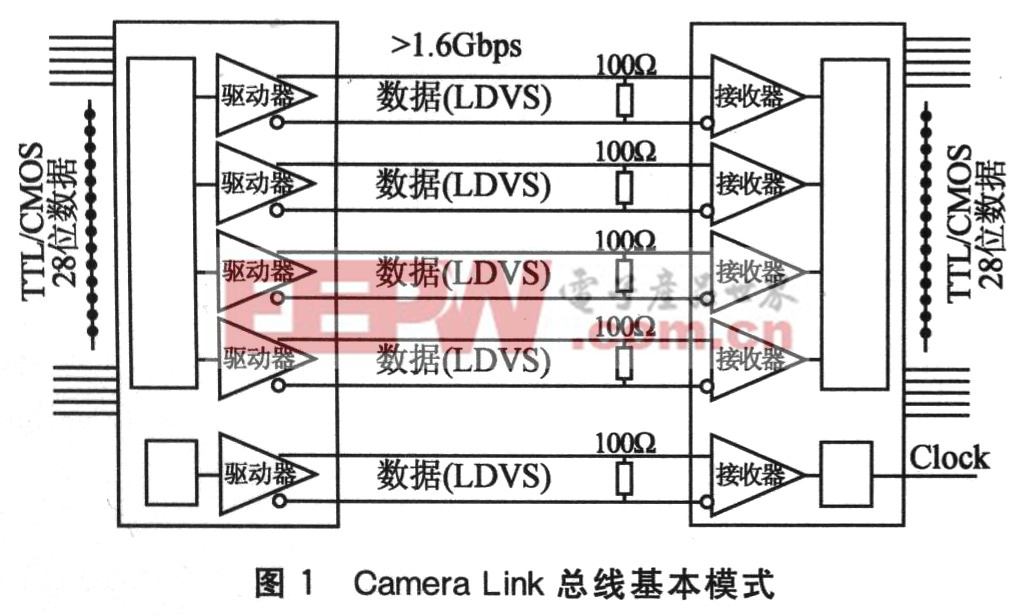

Camera Link是一種基于物理層的LVDS的平面顯示解決方案。圖1為Camera Link總線發送端與接收端的連接框圖,也是該總線的基本模式。總線發送端,將28位并行數據轉換為4對LVDS串行差分數據傳送出去,還有一對LVDS 串行差分數據線用來傳輸圖像數據輸出同步時鐘;而總線接收端,將串行差分數據轉換成28位并行數據,同時轉換出同步時鐘。這樣不但減少了傳輸線的使用量,而且由于采用串行差分傳輸方式,還減少了傳輸過程中的電磁干擾。本文引用地址:http://www.104case.com/article/191923.htm

3 高速數據采集卡Camera Link接口設計

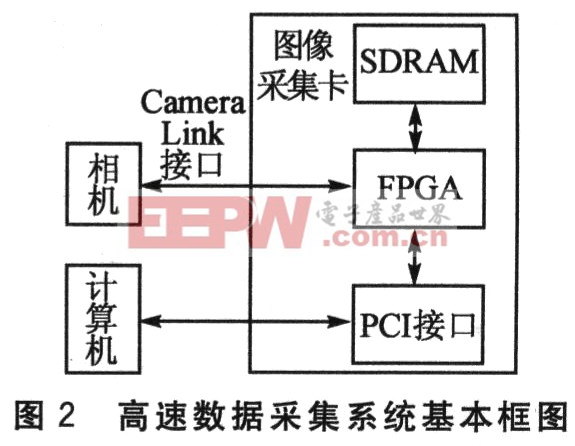

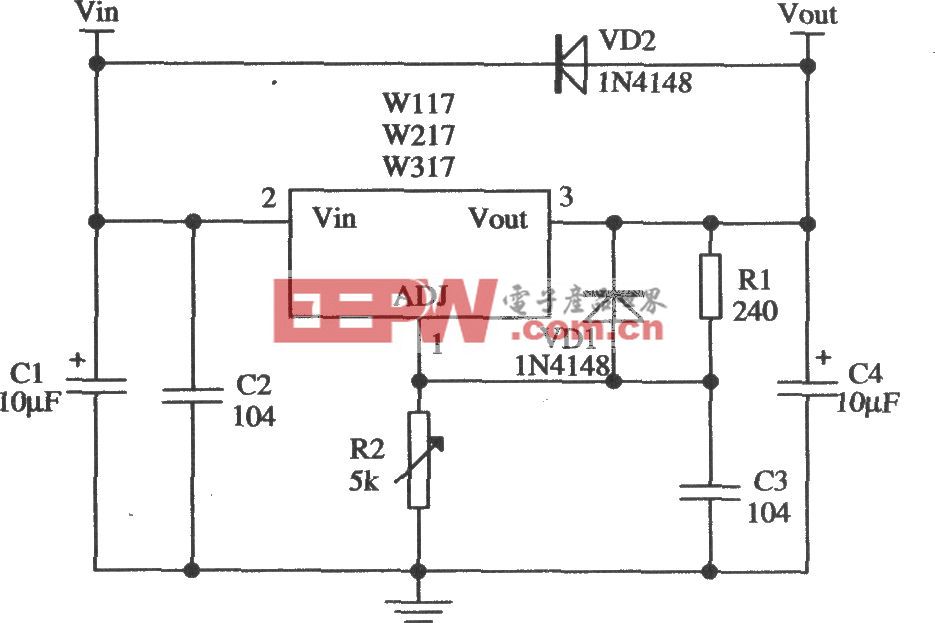

高速數據采集系統的基本框圖如圖2所示。FPGA給相機發出控制信號,相機中的數據通過Careera Link接口傳送到圖像采集卡;數據由FPGA讀入,緩存在SDRAM中。可以在FPGA中根據用戶的需求實現高速的圖像處理,根據圖像處理的結果可以由 FPGA完成用戶所需的控制。圖像采集卡通過PCI接口和計算機相連接,通過計算機可以配置圖像采集卡和相機,計算機也可以從采集卡中獲得圖像處理數據。接下來詳細研究FPGA和相機間的Camera Link接口技術。

3.1 DS-21-02M30相機的Camera Link接口

Camela Link總線標準規定:在完整模式下,最多可以使用8個端口(Port A~Port H)傳輸數據,每個端口為8位數據。DS-21-02M30相機使用Port A~Port C端口,用的是基本模式(Base)。相機后端有一個MDR26連接口,分別對應A、B、C三個端口各8位數據,加上FVAL、LVAL、DVAL和SP 四位數據控制信號,共28位并行數據位。

評論