采用VHDL設計的全數字鎖相環電路設計

2. 3 數控振蕩器的設計

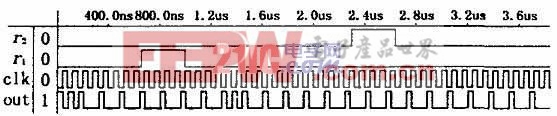

數控振蕩器由加/ 減脈沖控制器和除N 計數器組成的。加/ 減脈沖控制器其實是一個增量―減量計數器式DCO。它和環路濾波器連用。如果在環路濾波器無進位、錯位的時候,加/ 減脈沖控制器對時鐘2NFo 進行二分頻。當加/ 減脈沖控制的增量輸入端( I = 1) 輸入一個進位脈沖時, 輸出脈沖中通過該計數器內部加上一個時鐘脈沖。反之,當加/ 減脈沖控制的減量輸入端( D = 1) 時輸入一個借位脈沖輸出脈沖中就減去一個時鐘脈沖。因此通過借位和進位脈沖可以使輸出頻率得到改變, 輸出頻率能被進位和借位脈沖的最高頻率控制在一個給定的范圍內。加/ 減脈沖控制器由D 觸發器和J K 觸發器構成,根據功能分析,可以設計出相應的VHDL 程序。其運行后仿真波形如圖5 所示:

圖5 加/ 減脈沖控制器仿真波形圖

3 實驗仿真結果與分析

本設計中全數字鎖相環路采用軟件來實現的,通過用VHDL 語言編寫模塊,然后仿真,例化,逐漸由下而上的實現整個電路,最終達到整體仿真下載成功。

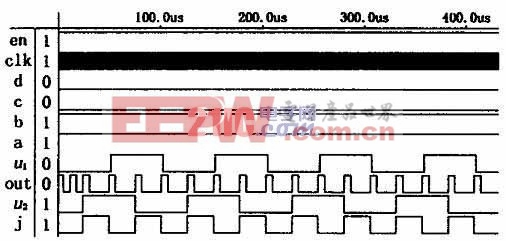

環路鎖定( k = 2^5) ,DPLL 系統仿真波形如圖6所示。

圖6 環路鎖定(取k = 2^5) 時的仿真波形

由仿真波形可以看出, u1 和u2 達到鎖定狀態時的仿真時間是70us。

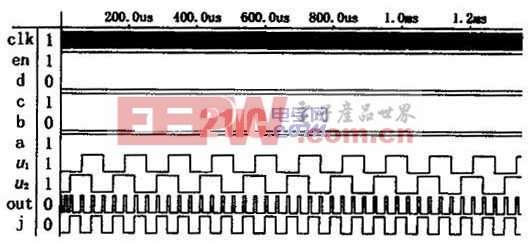

環路鎖定( k = 27) 時,DPLL 系統的仿真波形如圖7 所示:

圖7 環路鎖定(取k = 27) 時的波形仿真圖

在這種情況下, u1 和u2 達到鎖定狀態的仿真時間是180ms。

顯然,模k 愈大,環路進入鎖定狀態的時間越長。k 取得過大,對抑制噪聲、減少相位抖動有利,但是同時又加大了環路進入鎖定狀態的時間。反之, k 取得過小,可以加速環路的鎖定,而對噪聲的抑制能力卻隨之降低。

4 結語

采用VHDL 設計全數字鎖相環路,具有設計靈活,修改方便和易于實現的優點,并能夠制成嵌入式片內鎖相環。該類數字鎖相環路中計數器的模數可以隨意修改,這樣,就能夠根據不同的情況最大限度地、靈活地設計環路。

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 脈沖點火器相關文章:脈沖點火器原理 數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論