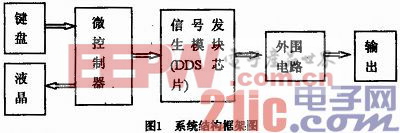

一種新型的正弦信號發(fā)生器的設(shè)計與實現(xiàn)

1.5 輸出信號調(diào)理部分

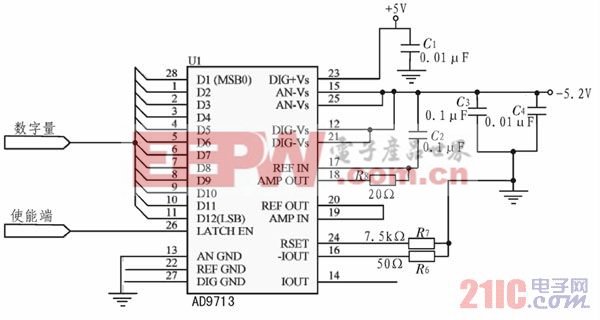

D/A轉(zhuǎn)換電路如圖7所示,選用的是12位高速D/A器件AD9713,該器件具有更好的靜態(tài)性能和動態(tài)特性。AD9713B更新速率可達(dá)100MS/ s。由于該D/A轉(zhuǎn)換器是針對DDS、波形重構(gòu)和高質(zhì)量圖像信號處理等應(yīng)用而設(shè)計的,這款芯片在動態(tài)特性方面表現(xiàn)特別突出,并且具有優(yōu)良的諧波抑制能力。AD9713輸出滿量程電流輸出是由VCONTROLAMP IN和RSET決定的,圖7中AD9713采用內(nèi)部參考電壓,輸出滿量程電流為-20 mA。

圖7 D/A轉(zhuǎn)換電路

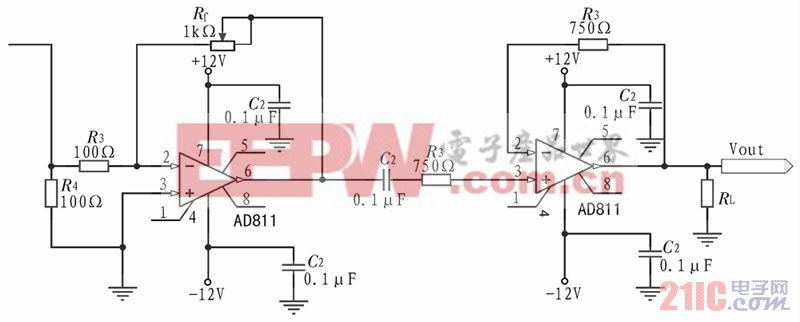

幅度調(diào)節(jié)電路是由放大器組成。高頻信號放大要求放大器有足夠的輸出電壓轉(zhuǎn)換速率,在正弦波的情況下,放大器所需要的最大擺率SR=2πω=2πAf,其中ω為信號的角頻率,A為信號幅度,f為頻率。此外,幅度調(diào)節(jié)電路要求帶低阻負(fù)載,放大器的電流輸出能力也是個重要參數(shù),要在50 Ω負(fù)載上輸出6 V信號,則放大器至少要有120 mA的連續(xù)電流輸出能力。考慮以上原因,本文選擇AD公司的高速運放AD811作為輸出放大器,它是一個寬帶高速電流反饋型運算放大器,其各項參數(shù)非常適合上述指標(biāo):小信號帶寬(G=+2時)達(dá)120 MHz,電壓擺率SR為2 500 V/μs,全諧波失真THD為-74 dB(10 MHz),輸出電流達(dá)100 mA,其短路輸出電流可達(dá)150mA。

幅度調(diào)節(jié)電路如圖8所示,圖中R3和R4起分流作用,限制用于I/V轉(zhuǎn)換的電流,1個電流反饋的高速放大電路。它把AD9713輸出的電流轉(zhuǎn)換成電壓,通過反饋電阻Rf的電流決定AD811輸出的幅度為6 V。為了增大后級的帶負(fù)載能力設(shè)計了后級電壓跟隨,模擬輸出的最后部分是濾波電路,濾波器的選擇主要取決于系統(tǒng)所要輸出的波形,在50 Ω的負(fù)載電阻上的電壓峰峰值為6±1 V。

圖8 幅度調(diào)節(jié)電路

1.6 頻率值的接收與顯示

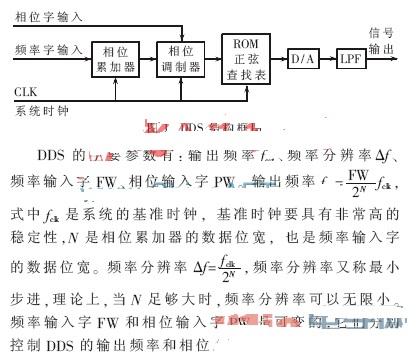

鍵盤、顯示部分用來實現(xiàn)用戶與單片機(jī)的交互。系統(tǒng)采用中斷查詢的方式接收通過鍵盤輸入的頻率值。該頻率值一方面送到數(shù)碼顯示接口進(jìn)行顯示,另一方面轉(zhuǎn)化成頻率控制字送往相位累加模塊。

2 系統(tǒng)軟件設(shè)計

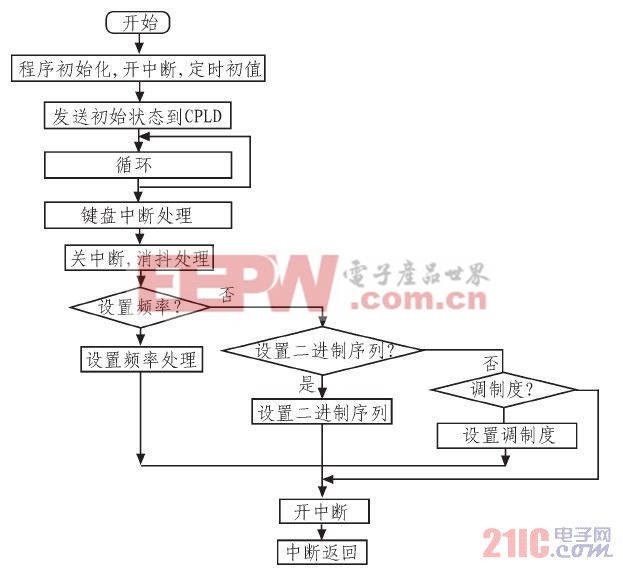

單片機(jī)程序采用C語言,在Keil uV2環(huán)境下編譯,用WAVE6000L仿真器調(diào)試CPLD在MAXPLUSⅡ下開發(fā),采用VHDL語言編程。

關(guān)于CPLD部分,相位測量儀和數(shù)字移相信號發(fā)生器采用ALTERA公司的EP1K30TC144-3FPGA芯片,原理圖已經(jīng)在前面的分析中。關(guān)于單片機(jī)部分,程序流程圖如圖9所示。

圖9 程序流程圖

3 功能及指標(biāo)測試

利用測試儀器:EE1641B1型函數(shù)信號發(fā)生器/計數(shù)器,直流穩(wěn)壓電源GPS-3303C、60 MHz示波器TDS1002,高頻測試儀等對設(shè)計的信號發(fā)生器進(jìn)行性能測試。正弦波的頻率范圍、步進(jìn)、在50 Ω負(fù)載上的輸出電壓幅度,失真度測量如表1所示,頻率穩(wěn)定度測量如表2所示,步進(jìn)為10%的幅度調(diào)制測試如表3所示,調(diào)制信號為1 kHz的頻率調(diào)制測試如圖10所示,二進(jìn)制PSK、ASK如圖11和圖12所示。

表1 正弦波實驗觀察結(jié)果

表2 正弦波頻率穩(wěn)定度測試結(jié)果

評論