多路接口與E1協議轉換器設計與實現

對于沒有使用的空閑時隙,系統可以根據時隙分配寄存器的值識別空閑時隙。在發送端,默認發送全“1”數據,在接收端,拋棄該無用數據;對于一路接口數據不能完全填滿一個或多個數據時隙產生的半空時隙,采取循環發空包的方法來填充半空時隙,空包格式固定為“000 01111”。在接收端,檢測到這樣的空包數據,丟棄不用。

下面主要實現V.35,RS 449,RS 232三路接口與E1協議轉換的設計。通過三路接口與E1協議轉換的實現,驗證多路接口同時與E1協議轉換的可行性。本文引用地址:http://www.104case.com/article/191187.htm

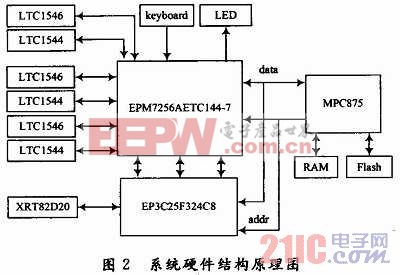

1.3 系統硬件原理框圖與模塊功能描述

系統硬件原理框圖如圖2所示,主要由接口芯片、FPGA、CPLD、微處理器構成。

LTC1546/LTC1544:多功能接口芯片LTC1546,LTC1544,二者結合,構成全功能的多協議接口界面,支持RS232,RS449,EIA530,EIA-530-A,V.35,V.36,X.21協議,協議的選擇可完全由軟件進行。

MPC875:飛思卡爾MPC875嵌入式CPU,基于POWERPC架構,主頻高達133 MHz,8 KB指令cache,8 KB數據cache,總線頻率最高可達80 MHz。

EP3C25F324C8:Altera公司的CycloneⅢ系列FPGA,性價比高,資源豐富。

EPM7256 AETCl44-7:A1tera公司MAX7000AE系列CPLD,支持多種接口電平。由于LTC1546,LTC1544接口電平為5 V,FPGA不支持這樣的接口電壓,這里使用CPLD作接口電路。

XRT82D20:RXAR公司的E1線路接口芯片,支持單路E1,具有HDB3編碼、時鐘恢復、線路驅動等功能,75 Ω或者120 Ω阻抗匹配。

keyboard:4×4鍵盤,用來接收時隙分配設置輸入。

LED:LED指示燈,共30個,用來指示30個數據時隙的使用情況:當LED燈點亮時,表示該時隙已經使用;LED燈不亮,表示該時隙為空閑。

評論