CPLD擴(kuò)展51單片機(jī)尋址范圍

引言:

本文引用地址:http://www.104case.com/article/190778.htm受其內(nèi)部資源的限制,在很多應(yīng)用中,單片機(jī)需要在片外擴(kuò)展相關(guān)資源,如程序存儲(chǔ)器,數(shù)據(jù)存儲(chǔ)器,IO口,以及中斷源等等。一般情況下51單片機(jī)地址線(xiàn)為16根(P0及P2),因此其地址空間為,也即64K。考慮到某些不需要高速度的應(yīng)用場(chǎng)合,可以用單片機(jī)的一個(gè)八位IO口(如P0),多次輸出地址,通過(guò)CPLD將這些地址位整合起來(lái),并輸出到相應(yīng)的設(shè)備,這樣,即可實(shí)現(xiàn)用單片機(jī)的一個(gè)八位IO口來(lái)實(shí)現(xiàn)多位地址的功能。

1. 51單片機(jī)擴(kuò)展FLASH存儲(chǔ)器

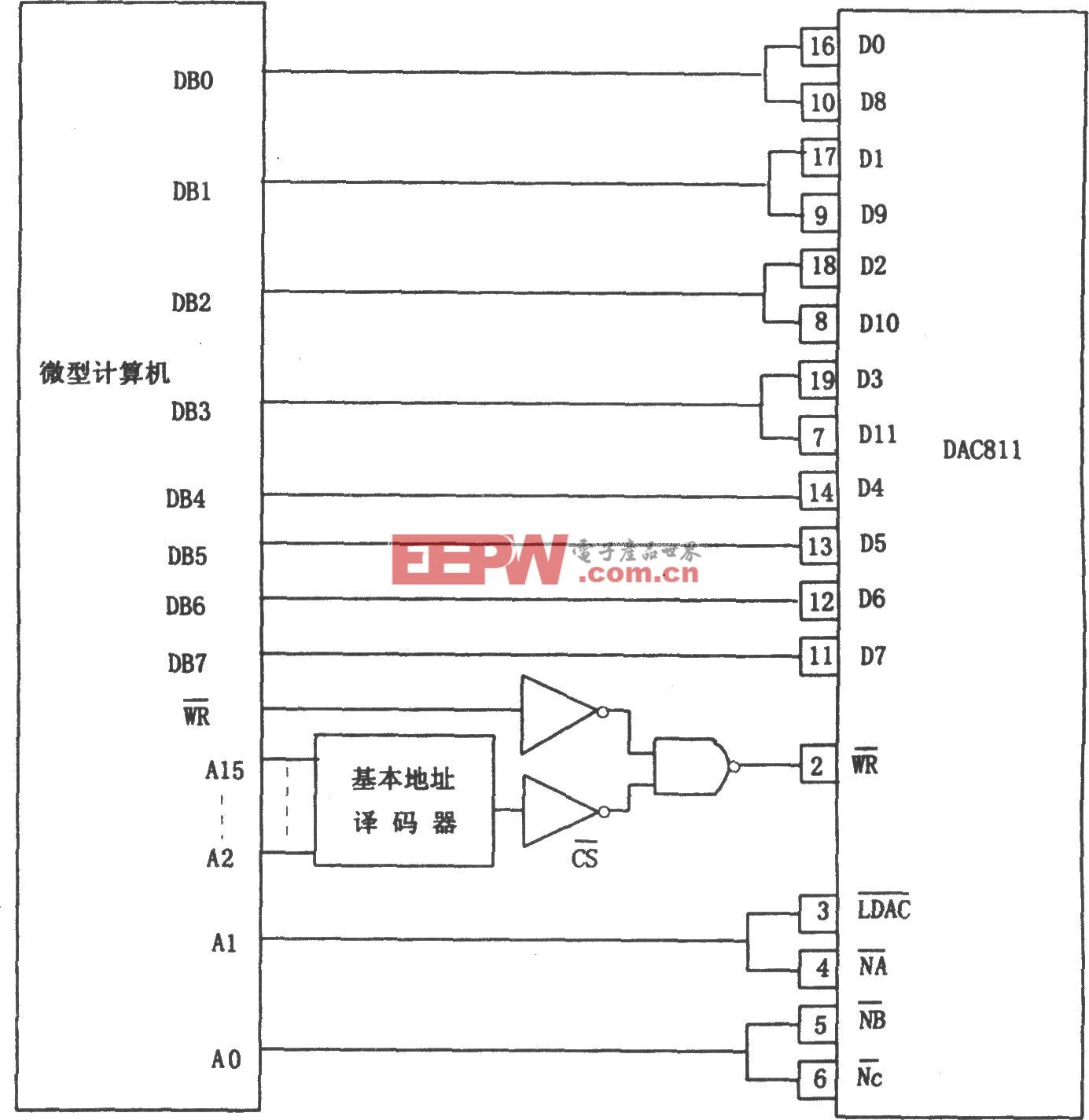

51單片機(jī)的系統(tǒng)擴(kuò)展以單片機(jī)的P2口作為指令地址的高八位,P0口作為低八位地址并復(fù)用為數(shù)據(jù)線(xiàn)。下面以擴(kuò)展ATMEL公司的AT29C020 flash芯片為例,該芯片地址線(xiàn)18根,容量為256K字節(jié),其讀寫(xiě)時(shí)序如圖1:

如果采用上述常用接法,則用P0口通過(guò)74LS373接AT29C020地址低八位,同時(shí)P0接AT29C020的八位數(shù)據(jù)口,P2接高八位地址,而AT29C020的A16,A17兩位地址位接P1.0,P1.1,從而由P1.0,P1.1與P0和P2口共同構(gòu)成18位地址線(xiàn)

由接線(xiàn)圖可知,對(duì)AT29C020進(jìn)行讀寫(xiě)操作時(shí),需先將P1.0和P1.1置成相應(yīng)電平,然后將低16位地址寫(xiě)入DPTR,再用指令 MOVX A, @DPTR或者M(jìn)OVX @DPTR, A 來(lái)讀或?qū)慉T29C020。

可見(jiàn),為滿(mǎn)足18位地址的AT29C020,單片機(jī)共用去了包括P0,P1,P2在內(nèi)的18個(gè)IO口,同時(shí)考慮到P3口一般復(fù)用為其他功能,如果系統(tǒng)還需要進(jìn)行其它的IO操作(比如將flash中的數(shù)據(jù)輸出到LCD顯示),硬件資源已經(jīng)是捉襟見(jiàn)肘。并且隨著存儲(chǔ)器的容量進(jìn)一步擴(kuò)大,IO資源將更加緊張。所以在下文中,將討論如何使用CPLD芯片來(lái)擴(kuò)展單片機(jī)的尋址空間。

2. MAX7128S CPLD

CPLD屬于ASIC,其內(nèi)部有大量的門(mén)電路,通過(guò)軟件編程可以實(shí)現(xiàn)這些門(mén)電路的不同連接關(guān)系,從而使CPLD對(duì)外完成不同的功能,而這些連接關(guān)系可以通過(guò)軟件的改變而不斷的改變。從功能上來(lái)看,CPLD可以完成任何數(shù)字器件的功能,上至高性能的CPU,下至簡(jiǎn)單的74電路。

目前,最大的兩家PLD/FPGA廠商分別是ALTERA以及XILINX,其中Altera 公司的產(chǎn)品基本上都屬于CPLD 結(jié)構(gòu)。由于它的內(nèi)部連線(xiàn)均采用連續(xù)式互聯(lián)結(jié)構(gòu),MAX 系列是Altera 目前最為流行,使用最廣泛的兩個(gè)系列之一。本文所采用的MAX7128S芯片就是屬于MAX7000S系列的一款CPLD芯片,它包含1800個(gè)可用門(mén),96個(gè)宏單元。

3. 相關(guān)硬件及接線(xiàn)示意圖

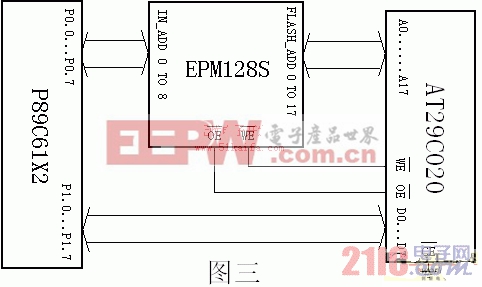

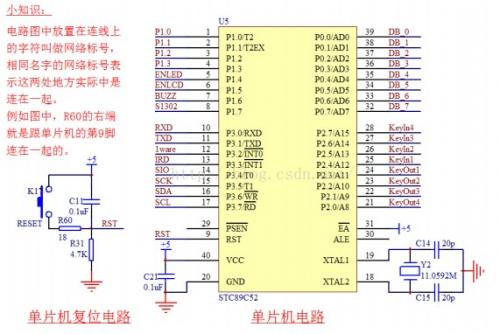

本應(yīng)用中單片機(jī)選用PHILIPS公司的P89C61X2,相關(guān)硬件連接示意圖見(jiàn)圖三

4.CPLD及單片機(jī)程序設(shè)計(jì)

在應(yīng)用中,將CPLD的4,5,6,8,9,10,11,12,15,16,17,18,20,21,22,24,25,27腳配置成連接 AT29C020地址線(xiàn),將46,48,49,50,51,52,54,55腳配置成接受單片機(jī)P0口地址數(shù)據(jù)的輸入口,并將41,44腳配置成連接 FLASH芯片的WE,OE引腳。

4.1 CPLD程序

本例中,采用硬件描述語(yǔ)言VHDL來(lái)編寫(xiě)CPLD程序,相關(guān)代碼如下:

entity mcu_to_flash is

port ( clk : in std_logic;

add : in bit_vector (7 downto 0); --地址輸入

flash_add : out bit_vector (17 downto 0); --地址輸出(到flash)

oe : out std_logic; --到flash的oe

we : out std_logic ); --到flash的we

end mcu_flash;

architecture func1 of mcu_flash is

signal counter : integer range 0 to 10000; --定義一個(gè)計(jì)數(shù)器

signal add_reg : bit_vector (17 downto 0); --定義寄存器add_reg用于緩存地址

begin

process (clk)

begin

if (clk'event and clk='1') then

case add(7 downto 6) is

when 00 =>

add_reg (5 downto 0) = add (5 downto 0); --地址0到5

counter = 0;

when 01 =>

add_reg (11 downto 6) = add (5 downto 0); --地址6-11

counter = counter + 1;

if (counter = 5) then --恢復(fù)OE,WE到高電平,為后面產(chǎn)生下降沿作準(zhǔn)備

oe = '1';

we = '1';

end if;

when 10 =>

add_reg (17 downto 12) = add (5 downto 0); --地址12-17

counter = 0;

when 11 =>

flash_add = add_reg; --輸出地址

counter = counter + 1;

if (counter = 5) then --產(chǎn)生OE,WE的下降沿

oe = '0';

end if;

end case;

end if;

end process;

end func1;

從程序可見(jiàn),本例中單片機(jī)需要寫(xiě)四次P0口進(jìn)行一次讀/寫(xiě)操作,且這四次寫(xiě)入P0的數(shù)據(jù)的高兩位應(yīng)該分別為 “00”;“01”;“10”;“11”,CPLD將該兩位作為標(biāo)志位判斷其后六位分別是所需地址的哪幾位,將前三次P0口數(shù)據(jù)的低六位“拼”成 FLASH的18位地址,并在第四次寫(xiě)P0口時(shí)將該地址輸出到FLASH的相應(yīng)地址位,同時(shí)由CPLD產(chǎn)生OE或者WE的下降沿信號(hào),以滿(mǎn)足FLASH的讀/寫(xiě)時(shí)序要求。

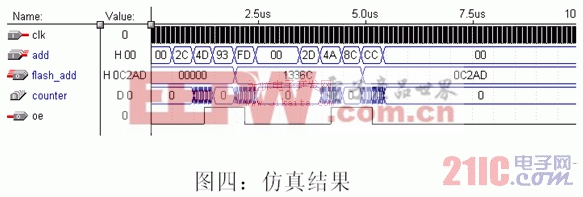

上述VHDL程序經(jīng)MAX+PLUS II仿真器進(jìn)行仿真,結(jié)果如圖四:

如圖,仿真中共有兩次讀操作。第一次操作時(shí)四次輸入的地址值(十六進(jìn)制)分別為:2C,4D,93,FD, 也即二進(jìn)制的“00101100”;“01001101”;“10010011”;“11111101”,如前所述,此時(shí)希望得到的地址應(yīng)該是 “010011001101101100”,換算成16進(jìn)制即為1336C,與仿真結(jié)果一致,同時(shí),在地址線(xiàn)(flash_add)得到地址值一段時(shí)間(時(shí)間值由程序中counter值判斷條件控制)之后,OE產(chǎn)生下降沿,與FLASH芯片讀寫(xiě)時(shí)續(xù)的要求一致。可以驗(yàn)證,第二次結(jié)果也和預(yù)期一致。值得注意的是,在仿真中,方便起見(jiàn)CPLD的時(shí)鐘輸入并沒(méi)有和實(shí)際硬件一致,故在實(shí)際應(yīng)用中,程序里面“counter”后一次判斷條件中的數(shù)值應(yīng)該保證能夠滿(mǎn)足FLASH芯片的時(shí)值要求。此外,針對(duì)本試驗(yàn),程序中只給出了OE的下降沿,實(shí)際應(yīng)用中,需要根據(jù)需要給出WE的下降沿。

4.2單片機(jī)程序

void Readflash (unsigned int add)

{char temp1,temp2,temp3; //定義三個(gè)變量緩存分三次輸入的地址

temp1=add; //低六位地址

temp1 = 0x3f; //將高兩位清零,作為第一次寫(xiě)P0口的值

temp2=add>>6; //中六位地址

temp2 = 0x3f;

temp2 |= 0x40; //將高兩位置為01,作為第二次寫(xiě)P0口的值

temp3=add>>12; //高六位地址

temp3 = 0x3f;

temp3 |= 0x80; //將高兩位置為11,作為第三次寫(xiě)P0口的值

P0=temp1; P0=temp2; P0=temp3; P2=0xc0; }

//寫(xiě)P0口四次,寫(xiě)完之后,AT29C020的數(shù)據(jù)端口即輸出有效數(shù)據(jù)。

可見(jiàn),函數(shù)Readflash的入口地址為FLASH芯片的18位地址,調(diào)用該函數(shù)后,F(xiàn)LASH芯片的輸出為該地址對(duì)應(yīng)的數(shù)據(jù),即可進(jìn)行下一步的操作。

5.實(shí)驗(yàn)結(jié)果

本例中,用單片機(jī)的P1口讀出該數(shù)據(jù),并用P2口輸出到8個(gè)LED,以判斷數(shù)據(jù)是否正確。經(jīng)過(guò)多次試驗(yàn),證明所讀出的數(shù)據(jù)正確無(wú)誤。(FLASH中已經(jīng)在實(shí)驗(yàn)前寫(xiě)入數(shù)據(jù))

6.小結(jié)

本文提出了一種用CPLD器件擴(kuò)展51單片機(jī)尋址范圍的思路,并通過(guò)實(shí)際驗(yàn)證可行。在實(shí)際應(yīng)用中,可以考慮用CPLD通過(guò)單片機(jī)固定的操作時(shí)間來(lái)判斷單片機(jī)的地址信號(hào)是所需地址空間中的哪一個(gè)部分,從而替代本例中所采用的標(biāo)志位,在不損失時(shí)間的情況下進(jìn)一步擴(kuò)大尋址范圍和應(yīng)用的靈活性。

參考文獻(xiàn)

1 周立功. 單片機(jī)與CPLD綜合應(yīng)用技術(shù). 北京. 北京航空航天大學(xué)出版社.

2 楊恒 FPGA/VHDL快速工程實(shí)踐入門(mén)與提高 北京. 北京航空航天大學(xué)出版社.

3 馬忠梅.單片機(jī)的C語(yǔ)言應(yīng)用程序設(shè)計(jì).北京:北京航空航天大學(xué)出版社

評(píng)論