基于可編程展頻時鐘生成器的降低EMI干擾技術介紹

控制和降低EMI的方法本文引用地址:http://www.104case.com/article/190640.htm

控制和降低EMI有兩個基本方法:抑制和吸收。最常用的降噪方法包括合理的設備電路設計、屏蔽、接地、過濾、隔離、分隔和定向、電路阻抗級控制、線纜設計和噪音消除等。

這些方法要求使用無源和有源元件,例如濾波器、扼流器、鐵氧體磁珠、箔片和??件,并結合PCB設計規則和展頻時鐘生成器(SSCG)。

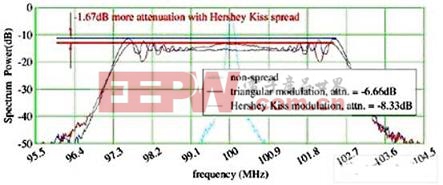

圖3:Hershey Kiss展頻概圖的優勢。

在源頭處解決EMI問題

EMC設計的一個基本原則是在PCB的源頭處減弱EMI。展頻法是指有意將特別帶寬中產生的輻射能量擴展到頻率域,產生一個帶寬更大的信號。展品時鐘生成器(SSCG)就可以執行這一功能。

在選擇展頻時鐘來減弱消費電子產品的EMI時,開發人員必須確保以下幾點:

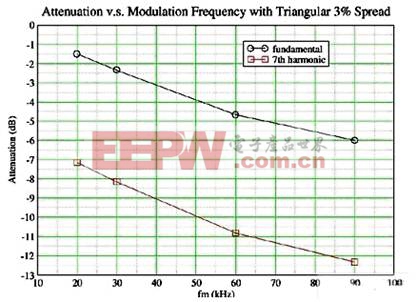

1) 系統必須通過EMI型式測試。良好的頻率概圖和調制頻率是最重要的。高質量的Hershey Kiss頻率概圖在降低EMI上是性能最好的;與之相比,三角頻率概圖需要更大的擴展量才能將EMI降低到同樣等級(見圖1至圖3)。調制頻率越高,就能將EMI降到更低的程度(如圖4)。

2)即便展頻有副作用,也要保持系統性能。首先,PLL必須運行于一個理想狀態,例如較高的PFD和VCO頻率和適當的帶寬等等。第二,頻率擴展量必須盡可能小,以便保持較高的系統時序余度和較低的周期間抖動。頻率擴展量更小,系統的平均頻率就不會降低太多,因而系統的運行速度也就不會那么慢。

3)要將對系統總成本的影響最小化。在消費電子產品中,展頻時鐘芯片的價格向來是一個主要的價格問題。但是,在最近幾年消費電子產品復雜性越來越高的同時,開發人員也要慎重考慮開發成本和風險。

比如,在抑制EMI和抖動中即便只有一項要求沒有達到,消費電子產品的系統時鐘需要調整的可能性就更大。可編程型抑制EMI的方法的靈活性,可以大大降低開發成本和風險,從而確保滿足所有要求。

圖4:通過調制頻率降低EMI。

展頻時鐘生成器

展頻時鐘生成器(SSCG)可分成可編程和不可編程兩種,也可以根據其是否有Hershey Kiss頻率還是三角展頻來分類。不同消費電子產品的展頻時鐘對于頻率、中心或向下擴展、擴展量、調制頻率、Hershey Kiss或三角展頻等的要求是不同的。

由于非可編程式展頻時鐘芯片是為特殊應用定制的,頻率范圍和擴展量只有幾個固定的可選項,要在最大化成本/性能的同時滿足最優展頻要求,就變得非常困難。

市場上大部分固定功能的時鐘芯片都有多個固定的可選擇輸入頻率范圍(如20-40MHz, 40-80MHz和80-160MHz)以及擴展率(如0.5%, 1%, 2%和3%)。要實現優化,就需要兩套PLL參數,一套針對EMI抑制性能,另一套面向PLL性能。

評論