一種改進的對抗軟錯誤電路結構設計

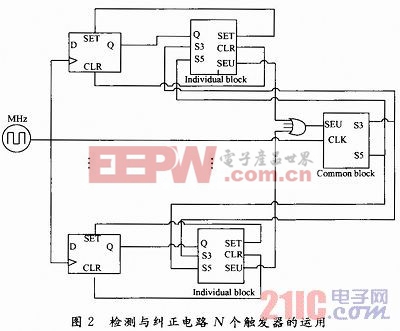

上述基于時鐘沿檢測和糾正電路是針對一個觸發器的情況,但是一個系統設計必定會包含多個觸發器。如圖2所示為該電路結構應用到多個觸發器的原理圖。電路結構可以分為獨立模塊和公用模塊兩個部分。時鐘是整個電路系統公用的部分,所以時鐘沿單元是可以公用的。此外,鎖存器是存儲前一個時刻的電路狀態,所以也是可以作為公用單元使用的。本文引用地址:http://www.104case.com/article/190562.htm

N個單獨模塊產生的錯誤檢測信號SEU_O,通過N位的或門輸入給公共模塊,進而對電路中N能發器的輸出進行修改。由圖2可知,任何一個觸發器檢測出有SEU錯誤產生,該觸發器的單獨模塊輸出信號SEU_O變為1,那么公共模塊的輸入信號SEU變為1,進而通過各個模塊的S5信號對狀態進行保存,使其對改變后的值不進行錯誤處理。

2 多次檢測單粒子翻轉的電路結構

由第一節可知,該方案雖然可以以較小的面積和使用較少的邏輯器件實現單粒子翻轉的檢測和糾正。但是它存在兩個問題,第一個問題是對于數據轉變沿的檢測只可以檢測0到1的轉變,不可以檢測到1到0的轉變,以至于對由于SEU引起的由1變為0的數據錯誤翻轉無法檢測,影響電路系統的穩定行;第二個問題是該電路結構設計的假設條件,每1個時鐘周期只發生1次單粒子翻轉引起的數據錯誤。由圖2可知,當一個時鐘上升沿來臨,鎖存器的輸出Q被清零,SEU_O的值只與數據沿和時鐘沿有關。當任何一個觸發器的輸出由于受到SEU的影響發生翻轉時,通過各個獨立模塊的錯誤檢測電路,檢測出有錯誤發生。此時,該獨立模塊的SEU_O變為1,并對該模塊中的觸發器輸出進行糾正。同時,公共模塊的鎖存器被置為1,由前面的式(2)可知。SEU_O變為0,并且與S3和S4無關,直到下一個時鐘上升沿到來時,鎖存器才被再次置為0,才會隨著S3和S4發生變化。由上述分析可知,該電路結構在一個時鐘周期內只可以檢測和糾正一次單粒子翻轉引起的數據輸出錯誤。

在只有一位觸發器的情況下,電路在每一個時鐘最多發生一次翻轉的假設是可以接受的。但是,隨著現在電路規模和功能要求的增加,這將限制電路對數據的檢測和糾正,嚴重影響電路系統的可靠性。

2.1 數據沿的產生

針對第一個問題,本文對數據轉變沿的檢測采用下述結構。該電路結構采用2個非門和1個異或門。利用兩個非門來產生延時,異或門對延時后的信號和原來的信號進行比較,進而在上升沿和下降沿時產生一個脈沖,用于數據沿的檢測。

2.2 多次檢測和糾正錯誤數據電路

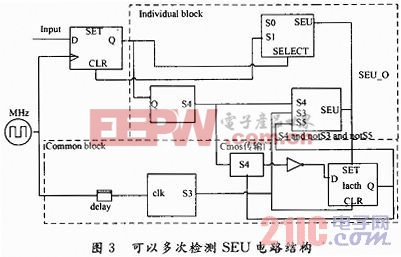

針對第二個問題,本文添加了少量的邏輯電路,以實現對由SEU引起的錯誤數據的多次檢測和糾正。原理圖如圖3所示,與參考文獻提出的電路原理相比,該電路結構只是在公共模塊上增加了1個非門和1個CMOS傳輸門,用于檢測數據修改是否完成,并對鎖存器賦值,使電路在數據糾正完成以后,讓鎖存器輸出變為0,即恢復到沒:有檢測到錯誤發生的狀態。該電路可以對下一個由SEU引起的數據翻轉進行檢測和糾正,進而大大提高電路的穩定性和可靠性。

電路原理:當時鐘處于上升沿時,信號S3產生一個高脈沖,此時鎖存器被清零。鎖存器輸出0時,CMOS傳輸門被關閉,不傳輸數據。當檢測到由于SEU引起的Q值翻轉時,SEU_O變為1,此時鎖存器被置為1。當SEU_O變為1時,對數據Q進行糾正,Q值發生翻轉,會產生一個高脈沖。當鎖存器被置為1時,CMOS傳輸門導通,SEU_O又變為0。數據Q被糾正,發生翻轉產生1個高脈沖,此時CMOS傳輸門被導通。數據Q產生的脈沖經過傳輸門和非門,變為低脈沖,該脈沖傳輸到鎖存器的輸入端,進而鎖存器的輸出變為0。此時,CMOS傳輸門關閉,信號SEU_O只與S4和S3有關,電路的錯誤檢測和糾正電路恢復到沒有發生錯誤時的狀態,準備檢測下一個數據沿。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論