邏輯器件的同步設計

在設計邏輯和電路時,經常會遇到這樣的問題。即采用普通集成電路實現的設計移植到FPGA/CPLD邏輯器件時,其設計無法正常運行。另外,有些設計己經在邏輯器件申實現或通過了仿真測試。但經過重新布線設計后,該設計不能正常工作。出現這些問題,基本上是在設計中出現了異步設計。典型的異步電路有以下幾種。

本文引用地址:http://www.104case.com/article/189900.htm(1)組合環路

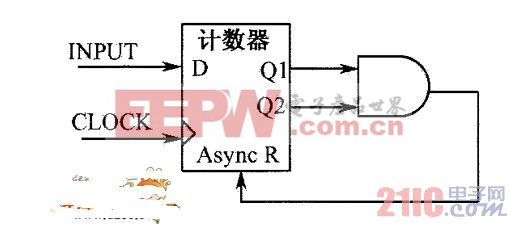

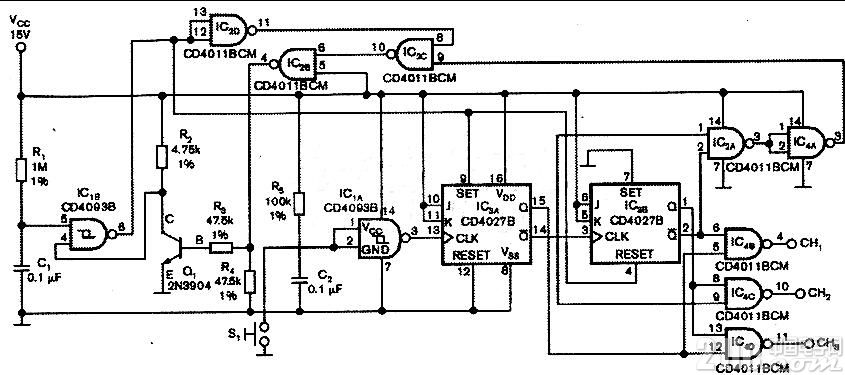

組合環路是數字邏輯設計中不穩定性和不可靠性最常見的原因之一。在同步設計中,所有的反饋環路都應該包括寄存器。組合環路直接建立沒有寄存器的反饋,違反了同步設計的原則。例如,當把一個寄存器輸出通過組合邏輯反饋給同一個寄存器的異步引腳時,就會產生組合環路,如圖1所示。

圖1 組合邏輯反饋的異步電路

組合環路是高風險的設計結構,這是因為組合環路的功能通常依靠環路邏輯的相對傳播延遲。正如所討論的,傳播延遲可能改變,那么環路行為也可能發生改變。

(2)延遲鏈路

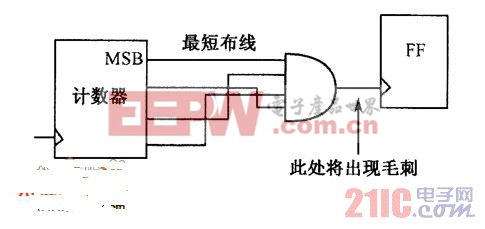

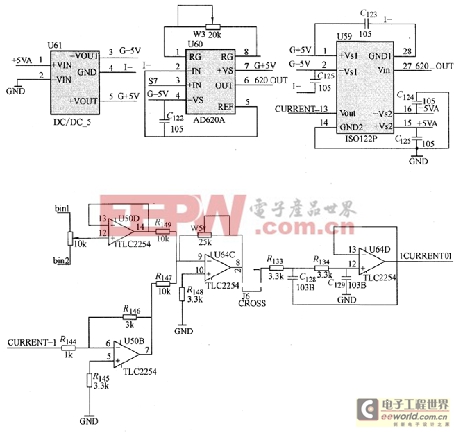

當兩個以上連續的單輸入單扇出節點引起延遲時就會產生延遲鏈路,通常把反相器連在一起增加延遲。延遲鏈通常由異步設計引入,有時用來解決其他組合邏輯引起的競爭冒險,如圖2所示。FPGA延遲會隨每次布局布線的變化而改變,延遲鏈可能引發不同的設計問題,包括增加了設計對工作條件的敏感性,減小了設計的可靠性,從而不利于移植到其他器件結構上。在設計中要避免使用延遲鏈,而應采用同步設計。

圖2 延遲鏈引發設計問題

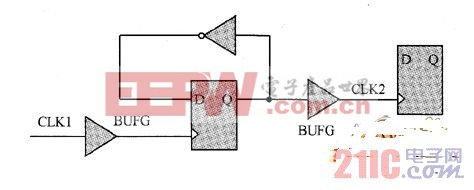

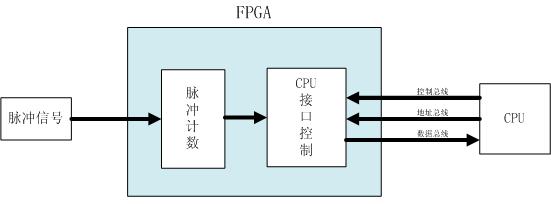

(3)異步計數器

在低速且小規模的集成電路設計中,經常采用異步結構進行計數器或分頻器設計,如圖3所示。因為這種電路結構簡單,連線較少。但這種電路結構非常容易產生競爭冒險現象,并且無法提供電路的工作速度。

圖3 異步計數器結構產生競爭冒險現象

綜合以上因素,為提高邏輯設計的可靠性,在邏輯設計時應盡可能地采用同步設計。另外,由于FPGA器件的內部結構特性,采用同步設計可以有效地利用器件中的邏輯資源。在同步設計時,只要邏輯延遲不等于或大于時鐘周期就可以避免毛刺對邏輯運行的影響,使系統穩定地同步于系統時鐘。

評論