基于FPGA技術(shù)的新型高速圖像采集

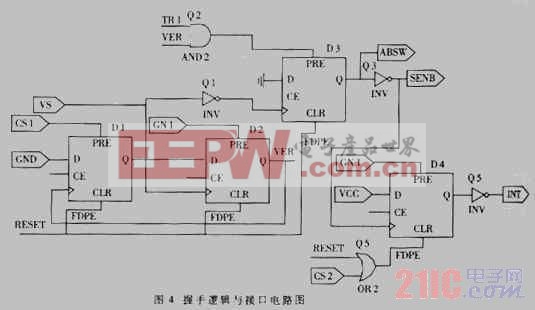

(2)握手邏輯是采樣控制器和CPU之間的接口,它是由幾個D觸發(fā)器及邏輯門實現(xiàn)的,如圖4所示。

當CS1(正脈沖)啟動采樣時,D1保存該信號,在下一個場同步脈沖到來時D2輸出高電平(即VER采樣使能信號)使行延遲計數(shù)器開始計數(shù),同時使D1復位,確保不再采第二場。當延遲計數(shù)器計數(shù)到預置值時產(chǎn)生觸發(fā)信號TRI(正脈沖),此時VER為“1”,則D3置位,輸出采樣使能信號SENB(低有效)和地址選通信號ABSW,使后面的電路處在采樣狀態(tài),在場同步脈沖下降沿D3翻轉(zhuǎn),整個采樣控制電路處在不采樣狀態(tài)。D2要在下一個場同步脈沖的上升沿才變?yōu)闊o效。

當SENB變?yōu)闊o效時(即SENB的上跳沿)觸發(fā)D4,使Q有效,向CPU發(fā)出中斷申請INT,CPU可用CS2清除這個中斷信號。

(3)RAM寫時序電路可根據(jù)芯片對寫操作的具體要求來設(shè)計。系統(tǒng)采樣頻率為13.5MHz即74.1ns),采用雙通道技術(shù)可使寫時序降低一半,寫頻率為13.5/2=6.75MHz即148.2ns)。SAA7111提供了27MHz的晶振頻率,則四個時鐘周期完成一個寫操作,時序的最小時間單位為18.5ns(半個周期)。根據(jù)RAM寫操作的要求,可以設(shè)計各種控制信號(WE、HS、VS、CS、SENB)、時鐘信號(CLK)、地址信號和數(shù)據(jù)信號之間的關(guān)系。本系統(tǒng)采用的RAM為IS61C1024,可以滿足系統(tǒng)需要。

采樣控制器擔負著重要的作用,是整個系統(tǒng)的核心;而同步控制邏輯又是采樣控制器的控制核心。同步邏輯起著協(xié)調(diào)行、場同步信號、地址計數(shù)時鐘、SRAM寫信號、采樣數(shù)據(jù)鎖存信號之間的時間關(guān)系、

保證SRAM寫操作時各信號的時序配合。由于采樣頻率高達13.5MHz,因此在硬件實現(xiàn)過程中需要不斷地模擬與仿真,有時要調(diào)整整個邏輯電路,計算延遲時間,解決電路中存在的競爭與冒險等等,這些都需要系統(tǒng)的可修改性好,具備可編程的特點。基于FPGA技術(shù)的ASIC設(shè)計滿足了上述要求,發(fā)揮了現(xiàn)場可編程的特點,降低了設(shè)計成本,縮短了開發(fā)時間,因此系統(tǒng)開發(fā)十分方便。

3 DSP處理技術(shù)

在此采集系統(tǒng)中,基于DSP的圖像處理技術(shù)也得到了應用,特別是在圖像的模式識別問題上充分發(fā)揮了DSP的硬件結(jié)構(gòu)和具有特色的編程指令。圖像模式識別的典型算法是卷積運算,也即乘累加,正好發(fā)揮DSP軟、硬件的特長。傳統(tǒng)的處理方法是基于計算機的硬件和軟件的,計算機完成一次乘累加運算需要11個機器周期,而DSP完成同樣的運算只需1個機器周期。本系統(tǒng)采用DSP芯片實現(xiàn)圖像的模式識別,提高了處理速度,解決了圖像處理過程中由于圖像識別速度慢而影響整個圖像的處理流程,解決了實際問題,收到了良好的效果。

評論