使用 PlanAhead Design 工具提高設計性能

PlanAhead 軟件提供了一種解決方案

本文引用地址:http://www.104case.com/article/189792.htm越來越多的客戶在賽靈思® PlanAhead™ 設計分析工具提供的層次化設計方法學中找到解決方案。PlanAhead 軟件為 FPGA 設計流程增加了可視性和控制。通過解決物理方面(介于邏輯綜合和實現工藝之間)的問題,您可在您的設計結果中實現性能的提高。

雖然先進的 FPGA 綜合產品為幾百萬門設計提供極高的自動優化水平,許多設計者仍需要具有更多啟發性的技術,以達到最佳性能目標。通過提供早期分析和布局規劃 (floorplanning)功能,PlanAhead 設計工具可以施加物理約束,以幫助控制設計的初始實現。實現后,PlanAhead 軟件可以分析布局和時序結果,以改進用于完成設計的布局規劃。您可以使用來自導入結果的物理約束,在后續實現嘗試期間鎖定布局。這些約束可用于創建可重用 IP,連同鎖定布局,一同用于其它設計。

PlanAhead 設計方法提供了性能、生產力以及結果的可重復性。憑借其層次化設計流程,PlanAhead 軟件可讓您減少運行 PAR 然后返回 RTL 與綜合的反復次數。相反

,您可以分析設計并在實現之前解決物理方面的問題。

更少的時間,更快的結果

PlanAhead 用戶通常可以實現 10-15% 的性能提升,有些用戶甚至可以實現更高。此外,設計者還發現他們可以在一個緊湊的器件中額外加入 10% 的邏輯。更快的性能與更高的利用率的結合意味著可以使用更小更便宜的器件,或者以更低的速度等級實現設計目標。

PlanAhead 設計工具可在縮短總設計時間的同時,還在結果中增加一定的一致性水平。通過利用以前的布局規劃或增量設計技術,您可以以更少的時間執行設計反復,實現可重復的結果。您還可以利用成功結果,將它們鎖定下來或在其它設計中重用。

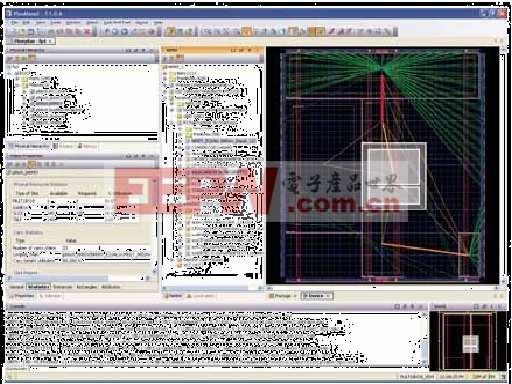

解決真正棘手的性能問題所需要的絕不僅僅是增加新的菜單項或腳本能力。PlanAhead 軟件通過使用各種視圖(見圖 1)展示設計數據,提供了一個完整的環境,使該層次化方法實現交互并易于使用。這些獨立的視圖可以相互結合使用,從而允許您快速識別和瀏覽關鍵設計對象和信息。

圖 1:PlanAhead 軟件提供了設計的不同視圖,以顯示物理層次、屬性、網表與約束、器件封閉引腳、原理圖及更多。

評論