可編程邏輯器件的應用參考

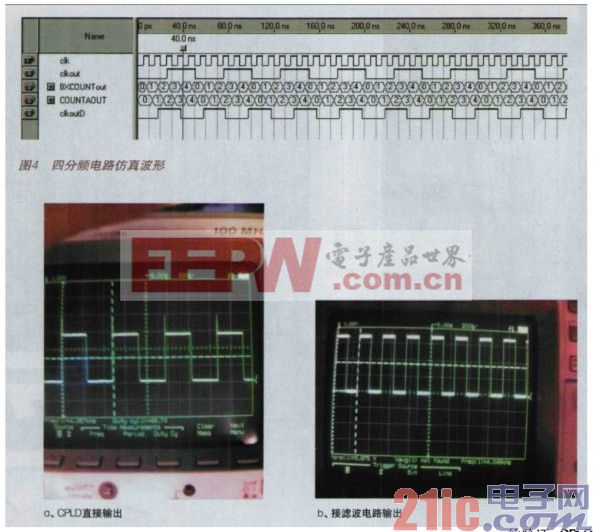

該程序仿真波形如圖4,實現了四分頻電路的邏輯設計、實現。

PCB電路設計

應用CPLD還需注意其輸出腳狀態改變時所產生的高頻的脈沖,會對下一級器件帶來嚴峻的考驗。因此在 PCB設計中必須進行相應的處理,才能有效抑制脈沖的極值,同時保證上升沿的陡直。圖5為一脈寬調制軟核的輸出效果圖。該模塊實現精度為8位的脈寬調制,方波信號基頻為4kHz,由33M的PCI時鐘分頻得來。系統只應用最簡單的阻容濾波電路來降低脈沖值。

該圖為直接輸出與濾波輸出兩種條件下的示波器顯示圖,在圖a中沒有采取濾波措施,可以看到在上跳沿處為4V左右的尖峰脈沖,相比穩定的高電平3V輸出高出1V。而圖b是經簡單的阻容濾波電路后輸出,上跳沿脈沖的峰值明顯得到抑制。較大的改善了系統的性能。

結束語

應用可編程邏輯器件,可加速開發的進程,在器件提供的方針環境中進行功能的仿真驗證,可及時發現設計中的缺陷。但是自帶的仿真器本身也并非完美,在電路設計完成后還需進行更細致的驗證。CPLD的廣泛應用給電子線路設計人員有更大的發揮空間,更靈活的設計方式,極大的提高了設計效率。

評論