基于CPCI總線的一體化數據處理中心的研究與實現

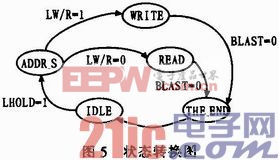

其中LHOLD、BLAST、LA[31:2]、ADS、LW/R等信號由PCI9656驅動,LHOLDA、LBE[3:0]、READY信號由FPGA驅動。通過模塊內部設計的狀態機實現對局部總線的控制,具體實現過程如圖5所示。本文引用地址:http://www.104case.com/article/189599.htm

1)IDLE狀態 系統上電或復位后,處于IDLE狀態。在IDLE狀態時,FPGA監測LHOLD信號,當單板計算機訪問FPGA時,LHOLD信號變為高電平。FPGA監測到該高電平后,立即使LHOLDA信號為高電平,轉入ADDR_S狀態。

2)ADDR_S狀態 在此狀態下,FPGA監測ADS信號,當ADS信號變為低電平,地址信號LA[31:2]有效,同時對輸入的讀寫信號進行判斷,若為讀操作,轉入READ狀態,若為寫操作,轉入WRITE狀態。

3)WRITE狀態 FPGA控制READY信號為低電平,以使總線上的數據有效,FPGA可以控制LBE[3:0]信號,以對傳輸的數據字節進行選取。并監測BLAST信號,當監測到BLAST信號為低電平時,表示傳輸最后一個數據,轉入THE_END狀態。

4)READ狀態 同WRITE狀態相似。

5)THE_END狀態 數據傳輸結束,FPGA監測BLAST信號變為高電平同時將READY信號變為高電平。當LHOLD信號變為低電平后,LHOLDA信號變為低電平,轉入IDLE狀態,等待下一次傳輸。

3.3 光纖通信電路和控制模塊設計

本設計中的光纖通信電路由并串轉換電路和光傳輸電路組成。并串轉換電路采用了TI公司的TLK1501芯片,通過內部的8B/10B編碼,將16位并行數據分成2個8位數據進行編碼,編碼后的數據為20位,再通過并串轉換發送出去;光傳輸電路采用FINISAR公司推出的FTLF1321SIM TL光模塊,將串行數據進行光電轉換輸出。

光纖通信模塊內部有一個狀態機,上電或復位后,處于IDLE狀態。模塊對傳送標志信號(TX_FLAG)監測,如果有傳送標志(TX_FLAG=1),轉入TX_READY狀態。在正常傳送數據前,需要對芯片進行同步操作,模塊控制信號TX-EN、TX-ER為00,連續發送3個空閑碼,使TLK1501進入

同步模式,狀態機轉入TX_S狀態。在TX_S狀態下,如果發送有效數據,模塊控制TX_EN、TX-ER為10,進行數據的正常發送,發送數據結束后,轉入IDLE狀態,等待下一次傳輸。在接收數據時,模塊監測RX-DV,RX-ER信號,如果RX-DV,RX-ER為10,正常接收數據。模塊設計的關鍵代碼如下:

4 結論

本文通過對多種功能接口電路進行研究分析,最終實現了在同一塊嵌入式板卡上集成光纖通信、A/D、D/A、CPCI總線、SDRAM存儲、FLASH存儲等功能。系統以FPGA芯片為處理核心,利用模塊化的思想進行設計,使系統方便擴展、易于維護和升級。經過長期的工程實踐驗證,本系統運行可靠穩定,能夠實現在復雜工業控制系統中對數據靈活控制、實時處理和高效傳輸。

評論