Hummingbird加密算法的硬件架構(gòu)設計

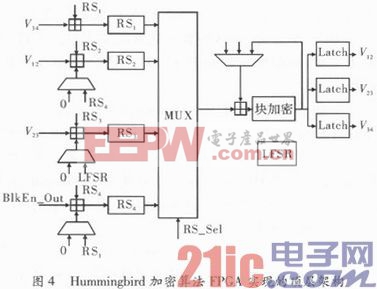

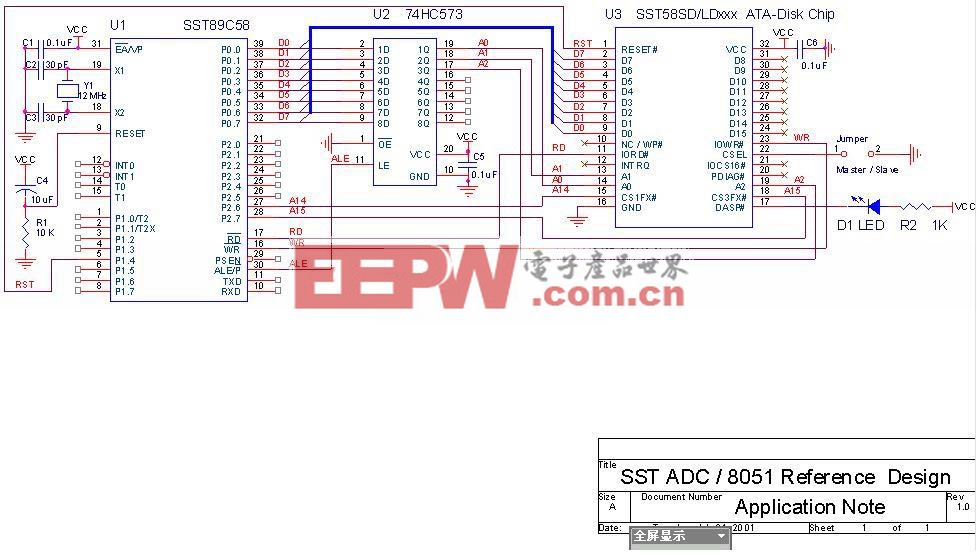

在這一架構(gòu)中,需要5個異或器、8個S—Box、一個線性變換過程及兩個多路選擇器。Hummingbird加密算法FPGA架構(gòu)的頂層設計如圖4所示。本文引用地址:http://www.104case.com/article/189549.htm

在頂層架構(gòu)中,塊加密的輸出首先被鎖存器鎖存,在初始化和每輪的加密過程反饋,以便更新狀態(tài)寄存器。由于初始狀態(tài)和每輪加密的狀態(tài)寄存器更新機制不同,因此需要數(shù)據(jù)選擇器來實現(xiàn)正確的更新,更新后的狀態(tài)寄存器在每輪加密過程中,分別輸入至塊加密過程。同時,由于初始化過程需要隨機數(shù)產(chǎn)生,因此,使用LFSR來實現(xiàn),以便節(jié)省硬件資源。

3 結(jié)果分析

文中使用Xilinx FPGA Spartan-3平臺,利用VetilogHDL來實現(xiàn)所提出的硬件架構(gòu)。將所提出的架構(gòu)和其他設計進行比較。文獻第一次提出了Hummingbird加密算法的FPGA實現(xiàn)架構(gòu),但其所需的硬件資源較多。文獻提出的方法雖然花費得硬件資源少,但速度較慢,同時需要更多的存儲器,實際所需的硬件資源并未減少。同時,文獻使用的是協(xié)處理器方法,并不能算作是硬件架構(gòu)。

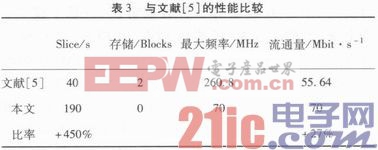

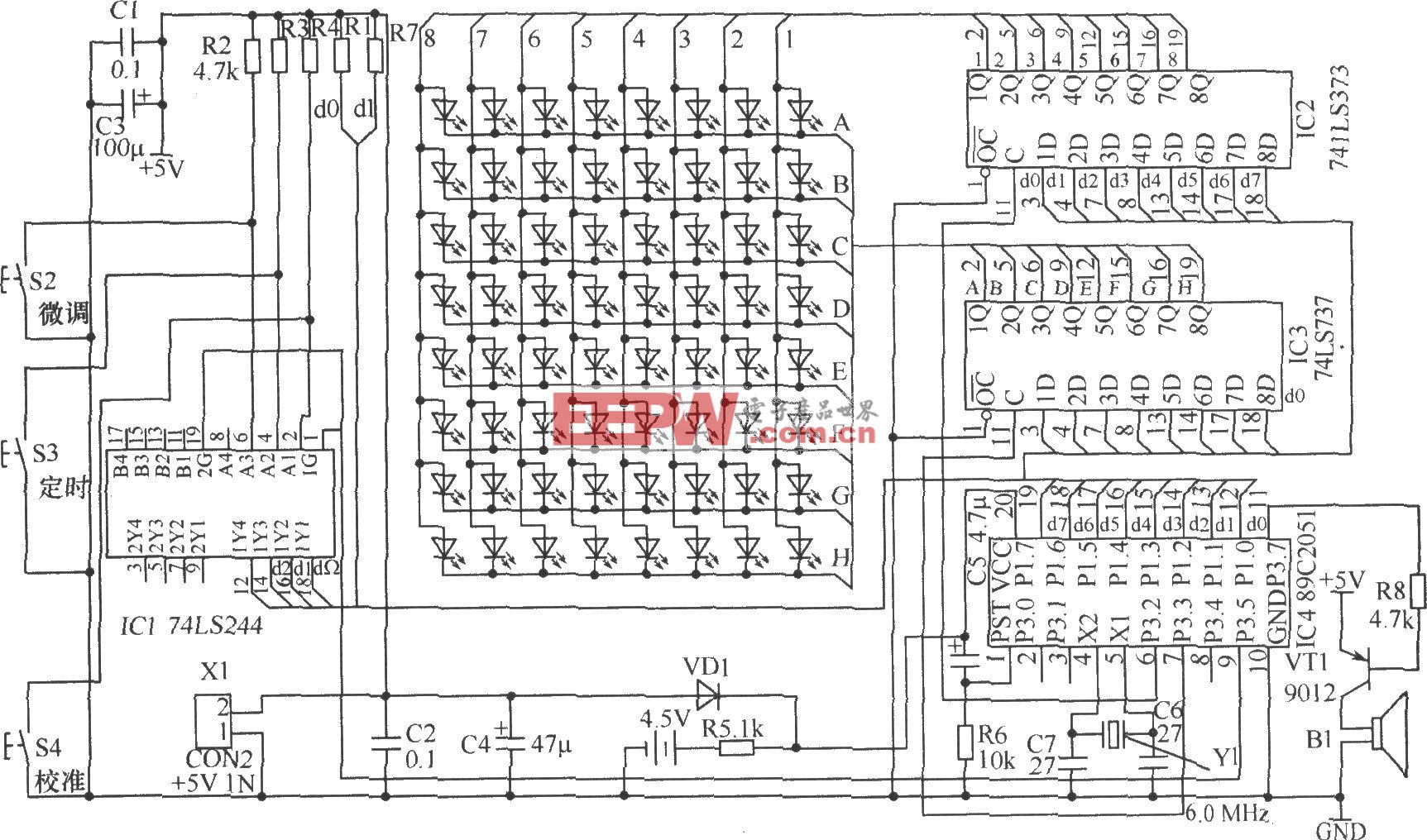

在表2中,給出了本次的方法和文獻的性能比較。

表2所示,提出方法所需的硬件資源比文獻少25%,同時速度也提升了6%。而在表3中,給出了文中的方法和文獻的性能比較。

相比于文獻,提出方法雖然所需的Slices數(shù)量較多,卻無需存儲器,同時速度可提升約30%。

4 結(jié)束語

文中提出了一種有效針對Hummingbird加密算法的FPGA硬件實現(xiàn)。該硬件架構(gòu)相比其他方法可使用更少的硬件資源,同時速度上也優(yōu)于其他方法。因此該架構(gòu)可廣泛用于RFID等硬件資源受限的加密平臺中。

評論