C波段寬帶低噪聲頻率源的研制

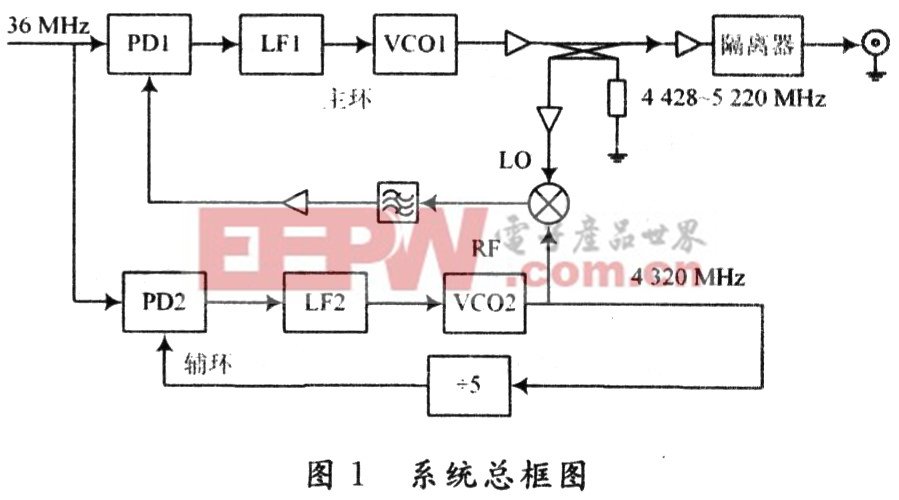

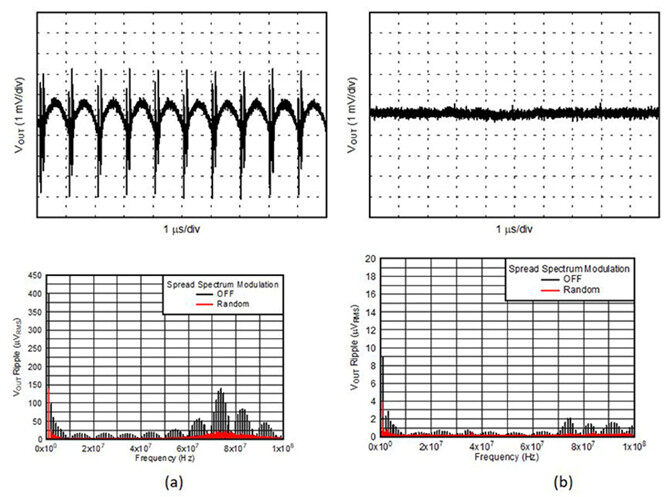

摘要:介紹了利用鎖相環和混頻技術,實現C波段低相噪跳頻源的方案,該方案通過兩個環路同時實現跳頻及混頻,步進36 MHz,輸出頻率4 428~5 220 MHz,具有低相位噪聲,低雜散等特點。和以往鎖相頻率合成的不同之處在于:以往混頻時采用主環信號4 428~5 220 MHz作為混頻器的RF端,而本方案為可以充分抑制輔環雜散,通過放大器將主環信號放大作為混頻器的本振LO端。測試結果表明達到系統對項目的指標要求,該頻率合成方案是可行的。

關鍵詞:雜散抑制;頻率合成器;低相噪;環路濾波器

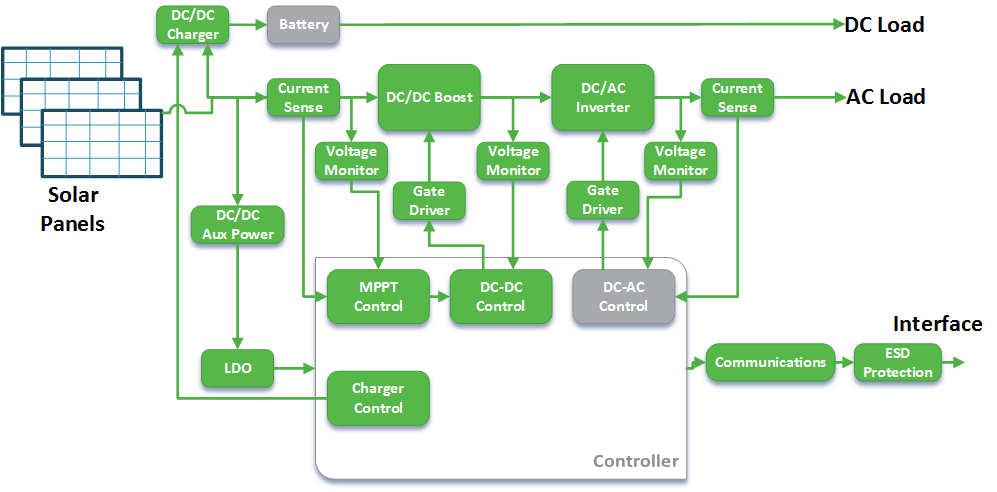

微波頻率源是微波通信、微波測量及雷達技術中的重要部件,其相噪性能和雜散性能直接影響到系統的性能和可靠性。因此,尋求更低相位噪聲、更高純度頻譜和更高穩定度的頻率源成為目前發展的主要趨勢。

l 系統主要指標及方案

1.1 系統的主要指標

輸出頻率范圍:4 428~5 220 MHz;步進頻率:36 MHz;相位噪聲:≤一100 dBc/

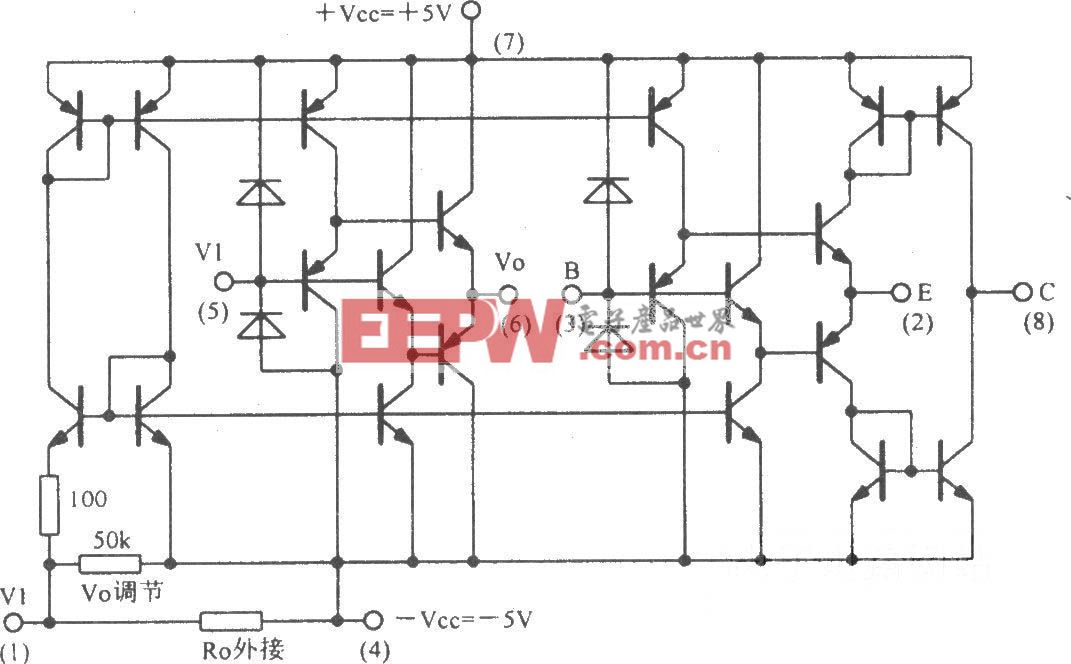

(3)由于對輸出在4 000~4 200 MHz帶內的雜散要求比較苛刻,而最佳輔環點頻為4 140 MHz,在腔體體積一定下,很難達到一70 dBc指標,故權衡輔環相噪的惡化程度,選擇4 320 MHz作為輔環。

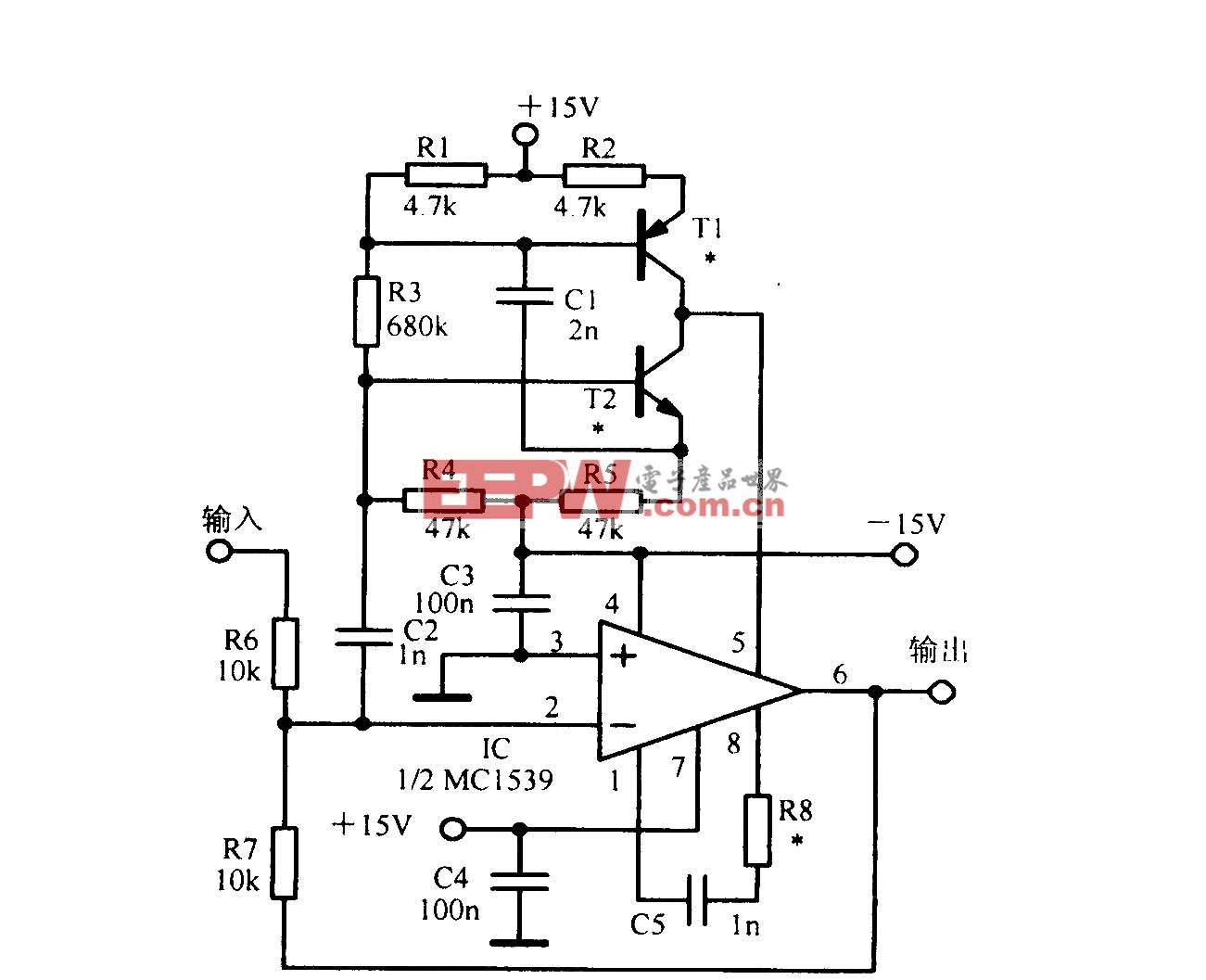

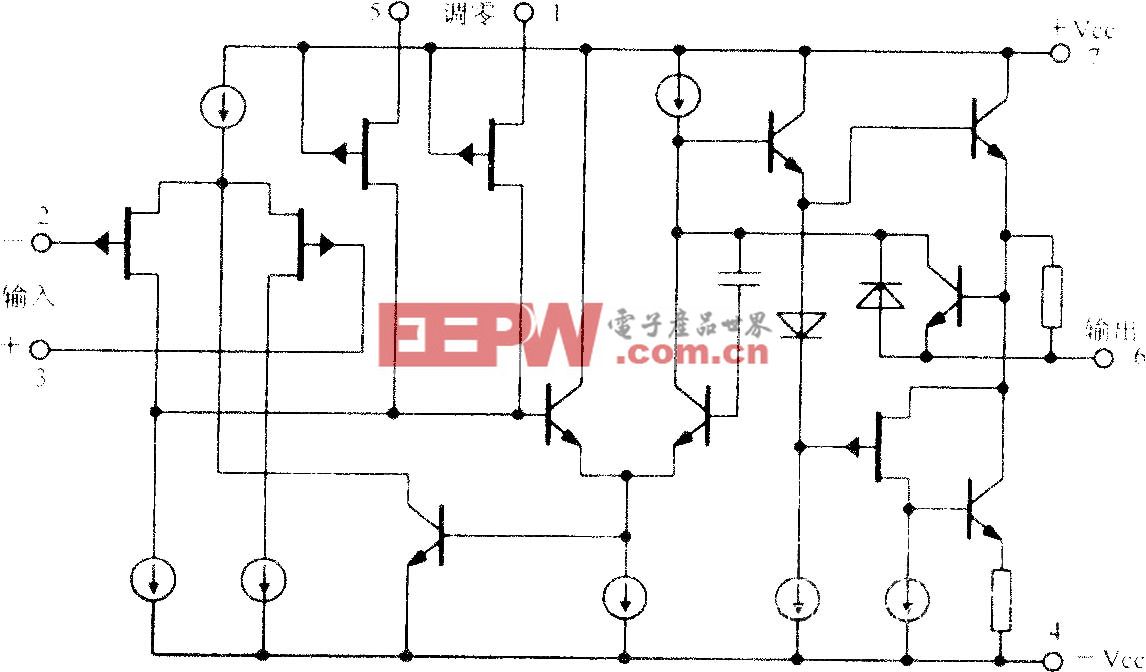

(4)為了防止輔環點頻4 320 MHz作為雜散耦合到輸出端,故采用功分器和將主環信號4 428~5 220 MHz通過兩級放大作為混頻器的本振,輔環4 320 MHz點頻作為混頻器的RF端。該方案選用36 MHz的低相噪恒溫晶振作為兩個環路的參考源,主環和輔環均選用HITTTITE公司的超低相噪模擬鎖相環芯片HMC440,改善系統的相噪性能。輔環參考頻率為36 MHz,輸出4 320 MHz頻點;主環參考頻率為36 MHz,輸出頻率為4 428~5 220 MHz。經定向耦合器后再與輔環輸出的頻點混頻到108~900 MHz,返回到主環鑒相器與參考頻率做比較。所有的控制都由單片機來完成,根據外部數據的輸入(BCD碼)來進行相應的頻率輸出。

2 電路實現

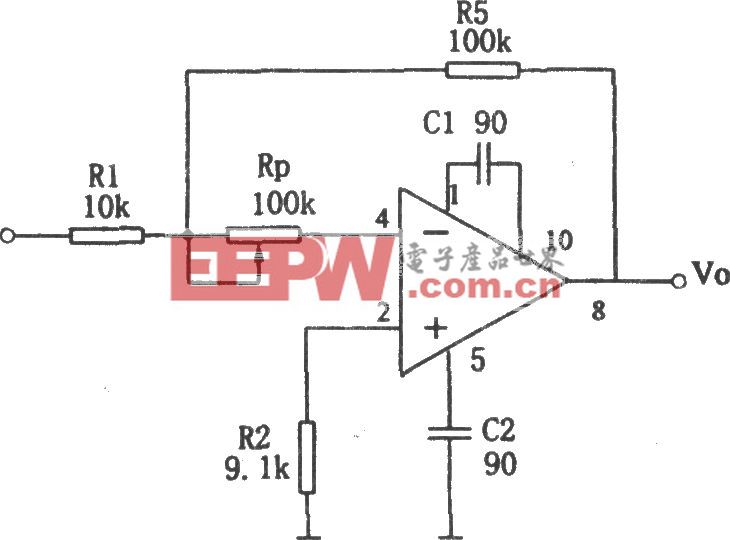

在設計單片頻率合成器的時候,最主要的工作就是設計頻率合成器的環路帶寬,使得頻率合成器指標在相位噪聲、雜散、調頻速度和穩定性上等方面達到兼顧,實現最佳的綜合性能。

2.1 最佳環路帶寬

由于本項目沒有要求跳頻速度,所以環路帶寬采用最佳帶寬設計,使得相位噪聲盡可能的好。頻率合成器的輸出噪聲如下:

![]()

式中Llp(jw)為鎖相環芯片的噪聲,Lvco(jw)為VCO的相位噪聲,Hn(jw)是被N規一化的環路濾波器的傳遞函數。由上式可以看出環路對帶內噪聲源呈低通過濾,故希望將環路帶寬fc越低越好;但環路對VCO呈高通過濾,又希望環路越寬越好。為了兼顧這一對矛盾,參考圖2能夠使兩種相位噪聲都得到合理的抑制,可以選擇環路帶寬fc在兩噪聲源譜密度線的交叉點附近總是比較接近于最佳狀態的。但是考慮晶振噪聲要惡化20log(N/R),所以實際帶寬要略小一些。

評論