采用FPGA的振動模擬器設計

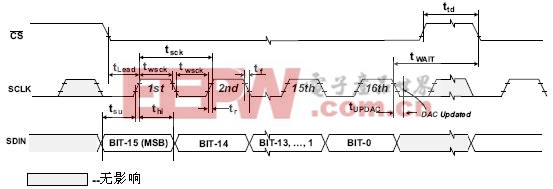

圖3 DAC8581 時序圖

圖4 DAC8581時序要求

4.1 FPGA對ADS1100芯片的控制

調頻和調幅信號使用同一款芯片:ADS1100,16位串行,I2C接口,在本設計中數據更新率是8SPS,電壓型輸出。此芯片僅可在從件模式下工作。ADS1100將模數轉換結果傳給FPGA模塊,由FPGA進行串并轉換。

FPGA對ADS1100提供SCLK和SDA引腳,符合I2C協議。FPGA是主器件,在開始與ADS1100通信前先對SDA寫2個字節,分別確定和哪個ADS1100進行通信和對ADS1100的配置寄存器(configuration register)進行寫以確定對其的操作模式。FPGA外接24MHz的晶振,經分頻得到4MHz的時鐘,ADS1100按8SPS的數據更新率工作,FPGA探測數據線變化以產生SCLK時鐘信號賦給SCLK引腳。篇幅受限,I2C的FPGA實現不一一贅述。

4.2 FPGA對DAC8581芯片的控制

信號輸出使用芯片DAC8581,16位串行,SPI接口,在本設計中最高數據更新率是1.8MHz,電壓輸出。DAC8581接收從FPGA傳送過來的串行數據,將其進行數模轉換,產生振動信號,模擬實際振動臺的理想振動情況。

FPGA中,由PLL倍頻得到36MHz的時鐘提供給DAC8581的SCLK引腳。由調頻信號計算得到串行DAC的數據更新率,按此頻率更新串行DAC的數字輸入。由同一個PLL倍頻得到240MHz的時鐘捕捉將由DAC處理的數字輸入信號和SCLK引腳信號的跳變沿,從而產生DAC8581的CS片選信號。

數據data一旦準備好,賦給register,240MHz時鐘探測到第一次SCLK上升沿,就拉低CS片選,第二次探測到SCLK上升沿時已經至少是下一個240MHz的上升沿了,從而滿足Tlead(見圖3、圖4)參數的要求。CS低時,一旦240MHz時鐘探測到SCLK下降沿,將register的最高位數據賦給SDA,將register左移一位,SDA保持不變,直到下一個SCLK下降沿。當捕捉到SCLK的第17個下降沿時,將CS拉高。由此即可滿足以上的圖3、圖4對時序的要求。

4.3 FPGA對DAC8820芯片的控制

DAC8820產生振動噪聲。16位并行,最高數據更新率4MHz,是電流輸出型。本系統設有2個用戶按鍵,分別表示產生40KHz~100KHz,100KHz~200KHz的噪聲頻率范圍,FPGA接收按鍵信號確定噪聲的頻率范圍,在此頻率范圍內產生一個隨機頻率,由此計算得到DAC8820的數據更新率,FPGA按此頻率準備數據以更新并行DAC的數字輸入。由DAC8820將其進行數模轉換,模擬實際振動臺在可能受到外界各種干擾信號后產生的噪聲情況。

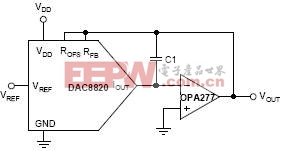

圖5 DAC8820外部電流電壓轉換電路

DAC8820的引腳WR(低有效)是將16位數據加載到輸入寄存器;LDAC(高有效)是將數據從輸入寄存器加載到DAC寄存器;但是若將同一信號同時賦給WR和LDAC,則可在下降沿將16位數據加載到輸入寄存器,在上升沿將數據從輸入寄存器加載到DAC輸出。

由FPGA將24MHz的晶振時鐘分頻得到數據更新率,由此得到的時鐘信號經高頻時鐘同步賦給DAC8820的WR和LDAC。由于DAC8820是電流輸出的,所以將電流輸出經過OPA277電流電壓轉換輸出,見圖5。圖中的C1是補償電容,其作用是防止增益峰值的出現。

5 結論

綜上,此振動模擬器的調頻信號的分辨率是16比特,可產生0 ~5kHz的清晰信號,所以頻率精度可達到0.076Hz,并可與200KHz以下的確定頻率范圍的隨機噪聲進行合成,輸出信號幅度分辨率可達16比特,而且噪聲的頻率范圍是可控的。

本文作者創新點:充分利用了FPGA可現場編程的特點,給讀者提供了一個實施簡單,成本低,可按用戶需求靈活改變,且易升級的振動模擬器的設計方案;且對有特殊要求的信號發生器的設計有一定借鑒意義。

評論