基于FPGA的LVDS高速差分板間接口應用

本設計當中,傳輸端AD板與接收端DSP板上的FPGA外部時鐘均為100 MHz,為了使用靈活可配置的接口工作速率,均采用DCM模塊對時鐘進行分頻/倍頻操作,可以將模塊工作時鐘在50~400 MHz進行靈活配置。

發送端采用Xilinx VertexlI XCl500 FPGA,速度等級為一5,DCM最高工作時鐘為420 MHz,接收端采用Xinlin Vertex4 SX55 FPGA,速度等級為一11,DCM最高工作頻率為450 MHz,經過驗證,在400MHz下工作良好。

為了得到最高400 MHz的時鐘頻率,須采取級聯DCM的方法,由第一級DCM產生50~200 MHz時鐘信號,第二級DCM產生200~400 MHz時鐘信號,BUFGCE為帶使能端的全局時鐘buffer,通過它選通200 MHz時鐘才能使第二級DCM中的DLL成功鎖定。

級聯及反饋方式原理圖如圖8,均采用DCM-ADV實例。本文引用地址:http://www.104case.com/article/188956.htm

第一級DCM例化參數如下,輸入100 MHz,輸出200 MH2,低速率模式:

值得注意的是,當傳輸模塊配置在最高時鐘頻率下工作時,需要對整個模塊進行比較細致的約束,才能使各模塊之間的延遲不至于引起傳輸數據錯誤。其中最關鍵的約束在于時鐘周期的全局約束以及對各個輸入輸出引腳的延時進行約束。限于篇幅,具體的約束方法不予贅述。

2 實現結果

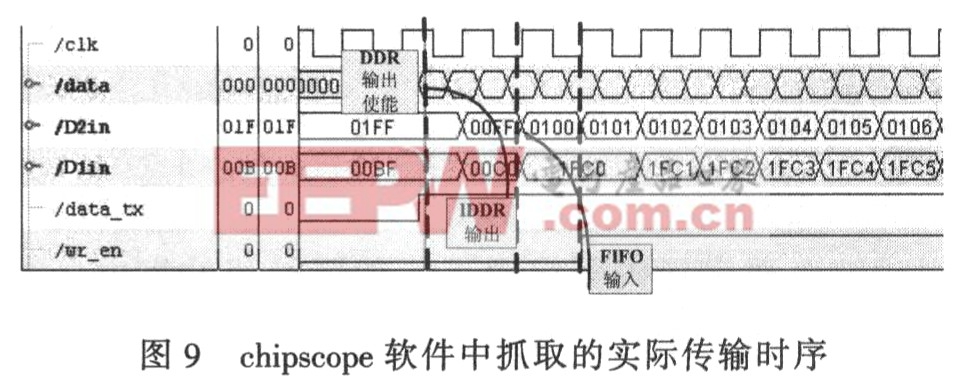

以下為ChipScope 9在線邏輯分析儀軟件捕捉的接收端波形。

Data為DDR輸入信號;D1in、D2in為經過IDDR模塊后從DDR信號中分離的兩路SDR普通信號;Data tx為傳輸控制同步信號,該信號有效時,傳輸開始;Wr en為傳輸控制邏輯生成的FIFO寫使能信號,因為Dlin、D2in信號須經過定點轉浮點模塊后再送到FIFO,所以FIFO寫使能需要比D1in D2in延后一個周期圖9用chipscope軟件在400 MHz采樣頻率下截取,此時傳輸接口工作在200 MHz時鐘頻率下,單線傳輸速率400MBit/s,接口工作速率為9.2 Gbit/s。

系統硬件平臺由AD采樣板和DSP板組成,通過高速接口互聯的平臺如圖10。

3 結語

本文在實現了一種高速的LVDS差分標準的板間數據接口,提出了具體的發送端與接收端系統框圖并最終在Xilinx FPGA器件上進行了實現,在圖10所示硬件平臺上工作情況良好,該硬件平臺的AD板為AD9218 105MSPS 10 bit采樣芯片和XilinxVertexII FPGA構成,信號處理板為Xilinx Vertex4FPGA和4片ADSP TS201 DSP芯片構成。

當采用最高系統時鐘400 MHz時,由于傳輸接口帶寬高達18.4 Gbit/s,使得高速AD和信號處理機之間不再有數據傳輸瓶頸,因此對于數字接收機性能,如瞬時覆蓋帶寬、實時性的影響全部來自于AD轉換器件性能和信號處理機的計算速度,從而解決了寬帶數字接收機內部的數據傳輸問題。

超級電容器相關文章:超級電容器原理

評論