雷達視頻信號模擬器的硬件設計與實現

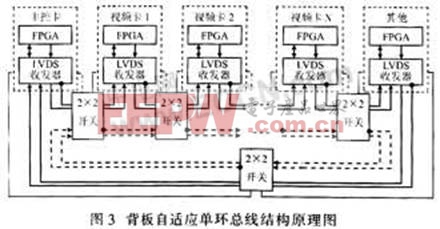

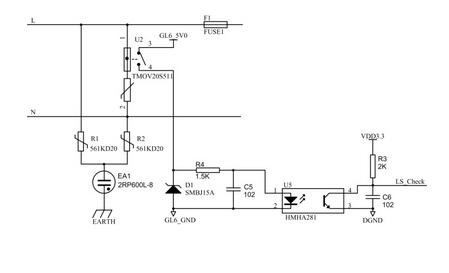

該系統需產生和差三通道I,Q共6路回波信號,而每路信號都需將對應的雜波、噪聲及目標參數下載到Flash存儲器中。由于數據量較大,且考慮到下載速度,該背板總線采用了自行設計的單環總線結構。該結構采用基于低壓差分信號收發器DS92LV18和低壓差分信號傳輸模擬交叉點開關SCAN90 CP02來實現。通過各子卡的插拔,實現對SCAN90 CP02的邏輯控制,從而保證無論背板各擴展槽是否有卡,整個環路都保持封閉狀態。DS92LV18的主要性能:15~66 MHz,18:1/1:18串行/解串器;收發一體設計;內置發射/接收數字鎖相環;提供幀同步、幀檢測、時鐘恢復功能;可進行單器件環路測試,器件引腳基本兼容,設有本地及線路環回模式。SCAN90CP02的特點:每通道的傳輸速率達1.5 Gb/s;低功耗;在雙中繼器模式下,最高速率時,電流為70 mA;低輸出抖動;配置有預增強功能,可驅動有損耗的背板和電纜LVDS/BLVDS/CML/LVPECL輸入;LVDS輸出。由這兩款器件組成的環網總線最大數據喬吐速度為1.188 Gb/s,能夠滿足快速下載數據的要求。圖3給出單環總線的結構原理框圖。

2.3視頻信號卡

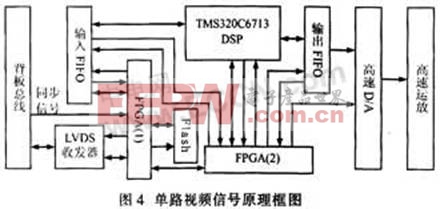

視頻信號卡為整個系統的核心部分,因其視頻信號的生成所涉及的運算量很大,單個DSP難以生成多路視頻信號,同時出于系統升級的考慮,因此該視頻信號模擬器的每路都使用高性能的TMS320C6713型浮點數字信號處理器。該DSP采用先進的超長指令字結構,內置8個獨立的功能單元、2個定點算術邏輯單元,2個浮點乘法器,4個浮點ALU、32個32位通用目的寄存器,4 K字節的L1高速程序緩存區,4 K字節的L1高速數據緩存器,256 K字節的L2兩級數據緩存器。這種結構能最大限度地發揮8個功能單元的并行計算能力,使得300 MHz系統時鐘工作下的DSP性能達到2400MI/s和1 800MFLO/s。

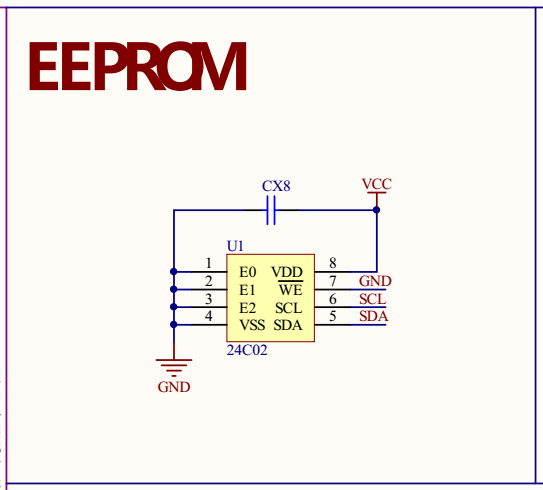

單路視頻信號生成原理框圖如圖4所示。其中,DSP完成視頻信號運算;FPGA(1)用于控制LVDS收發器接收來自總線上的命令、地址及數據,在產生視頻信號前,將上位機事先產生的雜波數據、噪聲及目標參數下載至Flash存儲器中。在生成視頻信號期間,FPGA(1)判斷DSP的工作狀態,將Flash存儲器的數據讀入輸入FIFO中;FPGA(2)主要完成DSP瀆寫輸入、輸出FIFO的邏輯轉換,接收來自DSP計算視頻信號相對PRF信號的延遲時間,通過FPGA(1)接收同步信號,讀取輸出FIFO的數據并啟動D/A轉換器;DSP將輸入FIFO的數據瀆人其內部RAM,根據對應的數據及目標參數生成所需的視頻信號數據,并將運算后的數據寫入輸出FIFO。FIFO采用IDT72V17160,其讀寫速度可達100 MHz。

3系統工作流程

上位機根據噪聲和雜波模型脫機產生和路、方位差、俯仰差三通道I/O雜波、噪聲及目標參數,由上位機發出指令、卡地址將各通道的數據下載至對應的Flash存儲器。然后,由上位機生成DSP指令,發送至主控卡的緩存中,觸發同步信號,將指令發送至DSP,同時視頻卡根據該同步信號產生視頻信號,DSP對視頻信號進行采樣、運算,并將其結果及狀態信息發送至上位機顯示。

評論