基于FPGA的航空總線協議接口設計

解碼模塊也可分為同步字頭檢測、數據解碼、串并轉換與奇偶校驗3部分。這個過程與編碼模塊相類似。

4.2 消息處理模塊

消息處理模塊主要是接收來自PC機的命令,并且將其運行結果上傳至PC機。為了能夠快速開發系統,采用EDK自帶的串口控制器IP Core。由于在Virtex-II Pro開發板上已設計與PC機相連的RS-232串口,并且配有標準的DB-9接口,因此只需通過IP Core 16450-UART控制器接收和發送數據即可實現系統與PC機的消息處理功能。

5 實驗結果

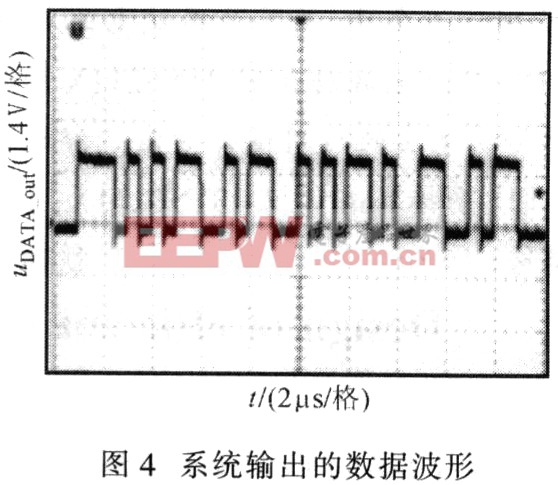

通過發送已知數據和示波器觀察實際接收到的數據波形,進行系統測試。測試中,輸入的十六進制數據為1234H,通過Tektronix公司的TDS3032B型示波器測試輸出數據,圖4是測得的系統輸出的數據波形,其中,波形前3位表示同步字頭,先負后正,表示發送的是數據字,正負電平各占1.5μs,中間的16位曼徹斯特碼恰好等于發送的1234H,而最后1位數據為奇偶位。因此測試結果證明:該系統設計能夠正確接收和發送符合1553B總線接口協議的數據,且工作穩定可靠。

6 結語

采用基于SoPC的設計方法,完成了MIL-STD-1553B航空總線接口邏輯的開發,并利用儀器測試系統。將該系統設計的總線協議接口邏輯固化到FPGA中。可取代國外進口的專用1553B總線控制器器件,從而擺脫長期依賴于國外進口器件的束縛,具有良好的軍事和經濟效益。該系統的創新之處是采用先進的SoPC技術開發FPGA,全面實現1553B總線接口邏輯,系統具有配置靈活,易于擴展等特點。

評論