2×8低噪聲InGaAs/InP APD讀出電路設計

在紅外通信的1 310~1 550 nm波段,高靈敏度探測材料主要有Ge―APD和InGaAs/InP APD,兩者相比較,InGaAs/InP APD具有更高的量子效率和更低的暗電流噪聲。In0.53Ga0.47As/InP APD采用在n+-InP襯底上依次匹配外延InP緩沖層、InGaAs吸收層、InGaAsP能隙漸變層、InP電荷層與InP頂層的結構。

APD探測器的最大缺點是暗電流相對于信號增益較大,所以設計APD讀出電路的關鍵是放大輸出弱電流信號,限制噪聲信號,提高信噪比。選擇CTIA作為讀出單元,CTIA是采用運算放大器作為積分器的運放積分模式,比較其他的讀出電路,優(yōu)點是噪聲低、線性好、動態(tài)范圍大。

1 工作時序和讀出電路結構

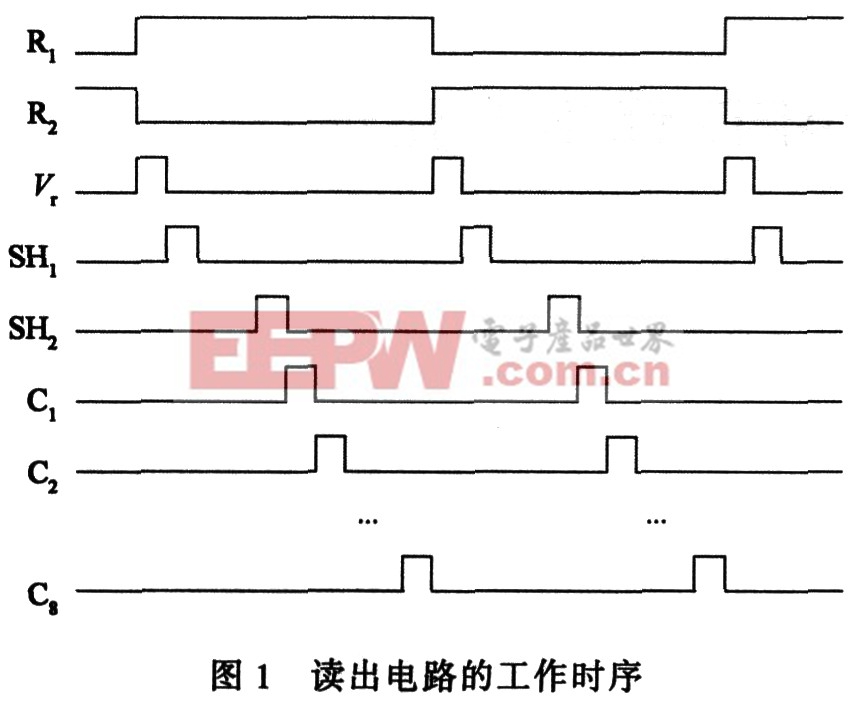

作為大陣列面陣的基礎,首先研制了一個2×8讀出電路,圖1給出了該電路的工作時序,其中Rl、R2為行選通信號;Vr為復位信號;SHl、SH2是雙采樣信號;C1、C2、…、C8為列讀出信號。電路采用行共用的工作方式,R1選通(高電平)時,第一行進行積分,SH1為高電平時,電路進行積分前采樣,SH2為高電平時,進行積分結束前的采樣,C1、C2、…、C8依次為高電平,將行上的每個像元上信號輸出;然后R2為高電平,重復上面的步驟,進行第二行的積分和讀出。

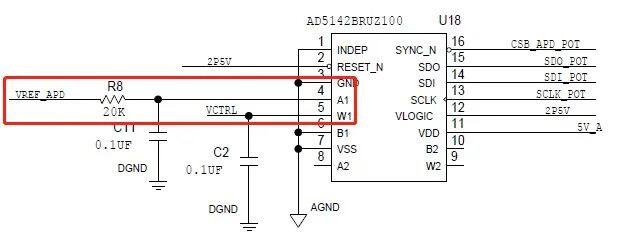

圖2是2×8讀出電路的結構框圖,芯片主要由行列移位寄存器、CTIA和CDS單元組成,圖中用虛線框表示:移位寄存器單元完成行列的選通,CTIA功能塊將探測器電流信號按行進行積分,CDS功能塊能抑制電路的噪聲,如KTC(復位噪聲)、FPN(固定圖形噪聲)等;FPGA主要產生復位信號(Vr)和采樣信號(SH1、SH2),觸發(fā)電路的復位和采樣動作,C8為該組信號的觸發(fā)信號,解決和芯片內行列選通信號同步問題。

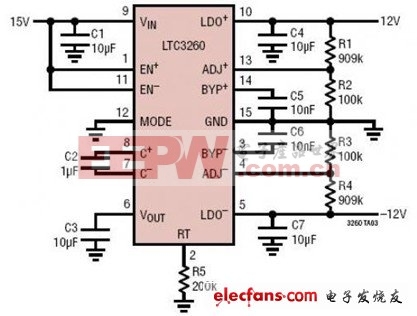

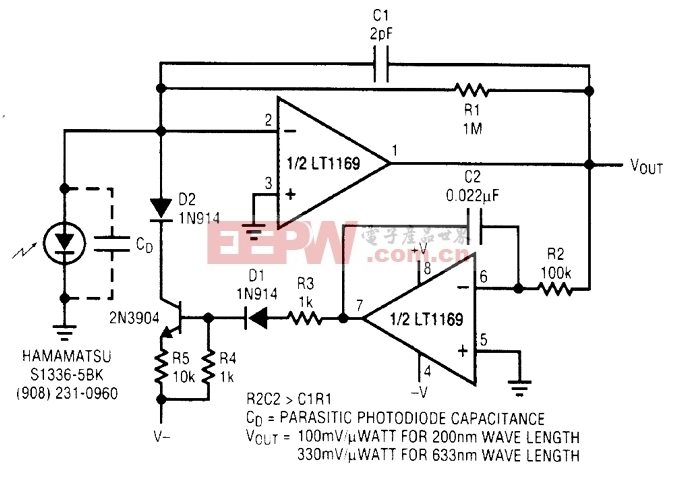

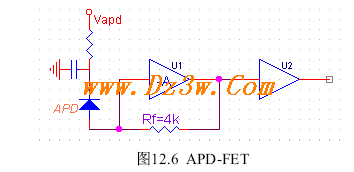

為了便于和讀出電路的連接仿真,首先根據(jù)器件特性建立了器件的電路模型,如圖3(a)中的虛線框所示,其中Idet、Rdet、Cdet分別表示器件的光電流、阻抗、寄生電容。圖3(a)還給出了CTIA讀出單元電路結構,主要由一個復位開關KR和積分電容Cint以及低噪聲運放A構成。在CTIA結構中,設計一個高增益、低噪聲、輸入失調小、壓擺率大的運放是確保讀出電路信噪比高、動態(tài)范圍大的關鍵。除此之外,積分電容Cint的設計也非常重要,在設計過程中發(fā)現(xiàn),選擇合適的積分電容也是關鍵之一。圖3(b)是CDS單元,由采樣管Ml、M2、采樣保持電容C1、C2及M3~M6構成的差分器組成,Vin為CDS輸入電位,也即CTIA的輸出電位。Voou1和Vout2為兩次采樣輸出,經過減法器后可以進行噪聲抑制。

2 積分電容Cint

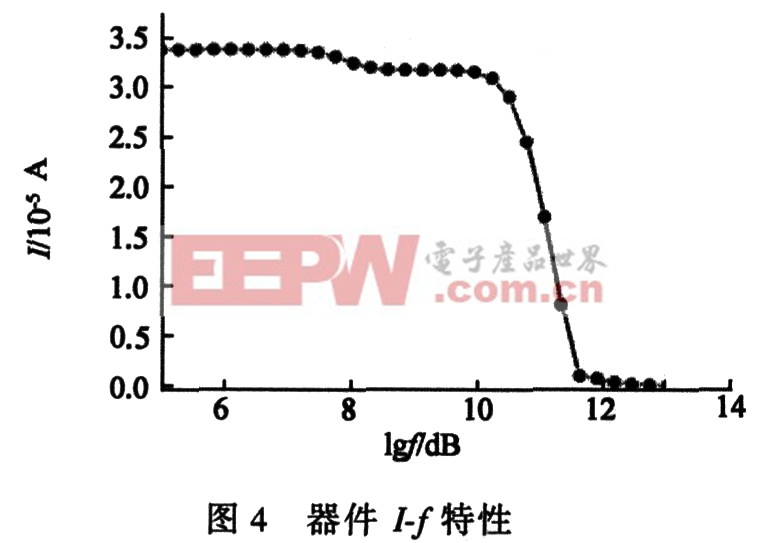

積分電容的設計主要和探測器信號電流的大小有關。圖4是In0.53Ga0.47As/InP APD特性,仿真結果顯示器件的工作電流一般在300 nA左右。

圖5為器件電流取300 nA時積分電容分別為2、4、6和15 pF時的輸出電壓Vout的仿真結果。仿真參數(shù)設計:在器件厚度為20 μm的情況下,根據(jù)器件仿真結果進行計算,器件阻抗為2×109Ω,器件寄生電容為80 pF。參考電壓Vb取2.0V,積分時間為60μs。可以看到對應不同的積分電容,積分電壓到達飽和的時間是不一樣的,也就是選擇不同的積分電容,最佳積分時間是不一樣的。如選用4 pF的積分電容,積分時間最好控制在40μs以下。

評論