基于AD9851的正弦信號發生器設計

1 引言

直接數字頻率合成DDS(Direct Digital Syndaesis)是實現數字化的一項關鍵技術,廣泛應用于電信與電子儀器領域DDS通常是在CPLD或FPGA內設置邏輯電路實現的,但由于DDS輸出受到D/A轉換器的速率及D/A轉換后I/V轉換中運放的帶寬增益和響應時間的限制,CPLD和FPGA內部實現方案在高頻段信號幅值已不穩定。因此,這里介紹一種基于DDS器件AD9851的信號發生器設計方案。

2 AD9851簡介

AD9851是ADI公司采用先進CMOS技術生產的具有高集成度的直接數字頻率合成器。該器件頻帶寬、頻率與相位均可控,內部頻率累加器和相位累加器相互獨立,32位調頻字使得其在180 MHz的系統時鐘下輸出頻率可達0.04 Hz的高分辨率。

設相位累加器的位數為N,相位控制字的值為FK,頻率控制字的位數為M,頻率控制字的值為FM,內部工作時鐘為FC,最終合成信號的頻率F相位和θ分別為:

F=FMFC/2N,θ=2πFN/2M

AD9851的最高工作時鐘為180 MHz,實際電路中,外部晶體振蕩器的頻率為25 MHz,由經內部集成的6倍頻器和高速比較器得到150 MHz的時鐘信號,這樣可減小高頻輻射,提高系統的電磁兼容能力。AD9851內部集成高速DDS和10 bit高速A/D轉換器,故無需D/A轉換和I/V,轉換等容易影響DDS輸出的單元。

3 系統總體設計方案

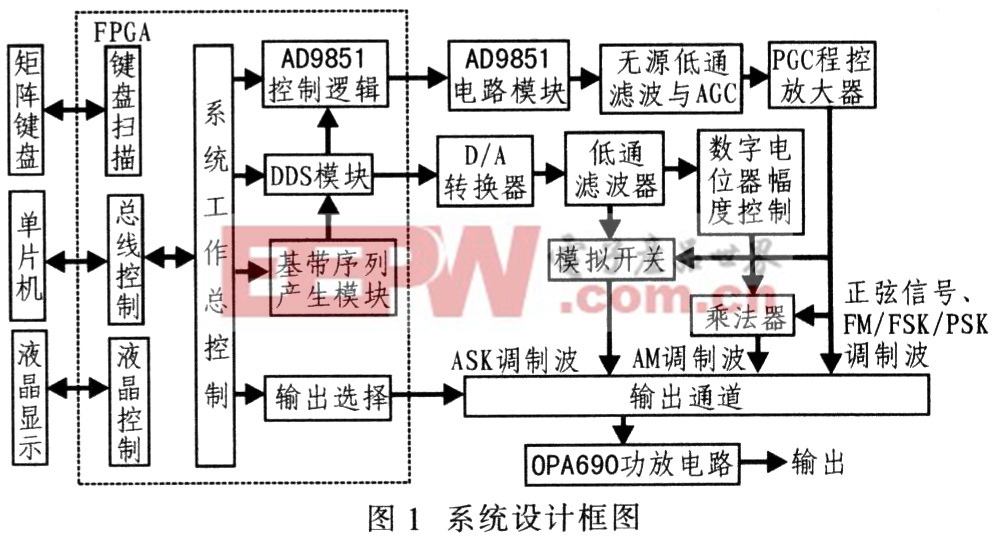

圖1為系統設計框圖。為了產生調制信號,需要在FPGA內部實現低頻段的DDS模塊以產生正弦波(模擬調制AM和FM)和二進制基帶碼(數字調制ASK/FSK/PSK)。由于AD9851輸出的正弦信號存在諧波,因此需加一個無源濾波器濾波。由于無源濾波的衰減特性,為使信號源的最終輸出信號幅值穩定,系統需加一級AGC電路。PGA程控放大器采用DAC7611作為基準控制輸出信號的幅度。AM電路采用模擬乘法器AD835構成,ASK調制較簡單,直接用DDS產生的二進制基帶序列控制模擬開關,從而控制AD9851信號的輸出。最后由多路選擇器和OPA690功放電路控制輸出。

評論