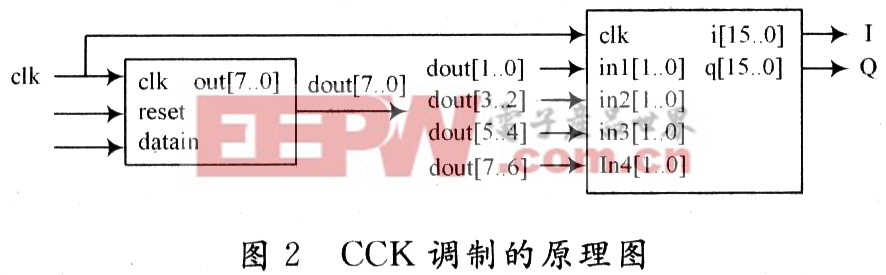

基于Cyclone Ⅲ的CCK調制、解調全新電路研究與實現

2.3 CCK的解調

2.3.1 最大似然解碼

在對CCK的進行解調時,一般可采用最大似然解碼器對碼字進行解碼,這里的最大似然(ML)解碼器是利用CCK碼字的良好的互相關特性,將接收到的受到噪聲干擾的碼字與64個可能的碼字進行相關運算,然后比較得到64個相關結果,并找出其中幅度值最大的那一個,由此對碼字作出判決。

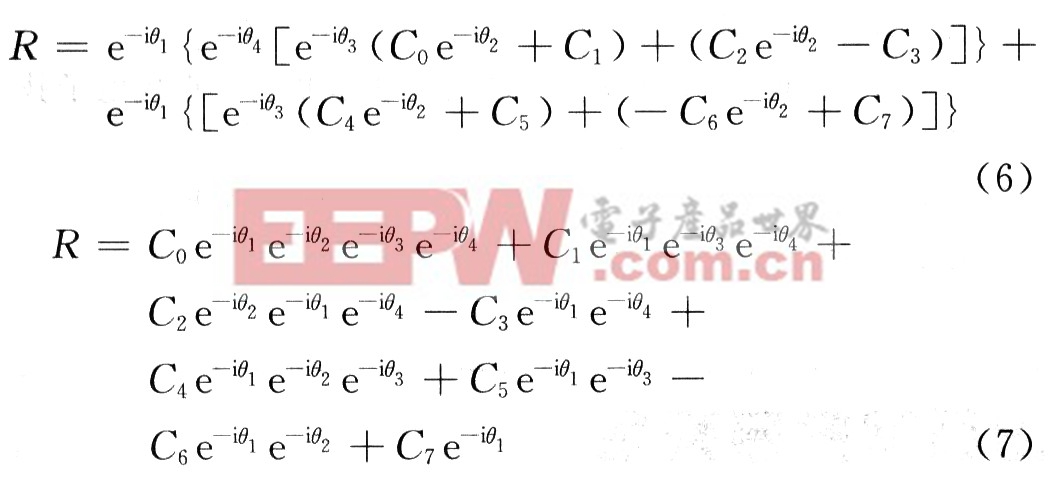

設接收到的CCK碼字為C'={C0,C1,C2,C3,C4,C5,C6,C7};Ci(i=0,1,…,7)表示接收到的數據,將其與所有碼字進行相關運算,則R=C'C*,C*是C的共軛,C是發送端的碼字,則:

式中:θi(i=1,2,3,4)表示角度;θ1~θ4遍歷{0,π/2,π,3π/2}。由式(7)可知,只有當θ2=φ2,θ3=φ3,θ4=φ4時,相關值會獲得最大值,為8,并由此解調出d7~d0的值。

2.3.2 新的解碼方法――選擇部分解碼

通過上述內容可以看出,如果對調制后的CCK碼字C'={C0,C1,C2,C3,C4,C5,C6,C7)中的每一位進行相關運算,并且在對每一位進行運算時,又對其中的θ1~θ4都進行遍歷{0,π/2,π,3π/2)的話,解調過程將是一個很復雜而又繁瑣的過程,同時它所帶來的計算量也將是巨大的。所以,這里提出一種全新的CCK解調方案。

這種全新的解調方案不像傳統的解調方案那樣對每個CCK調制后的碼字進行相關運算,再根據相關值最大來判斷出相應的CCK碼,而是只對部分的調制后的CCK碼字進行相關運算,并根據相關最大值解調出全部的CCK碼。

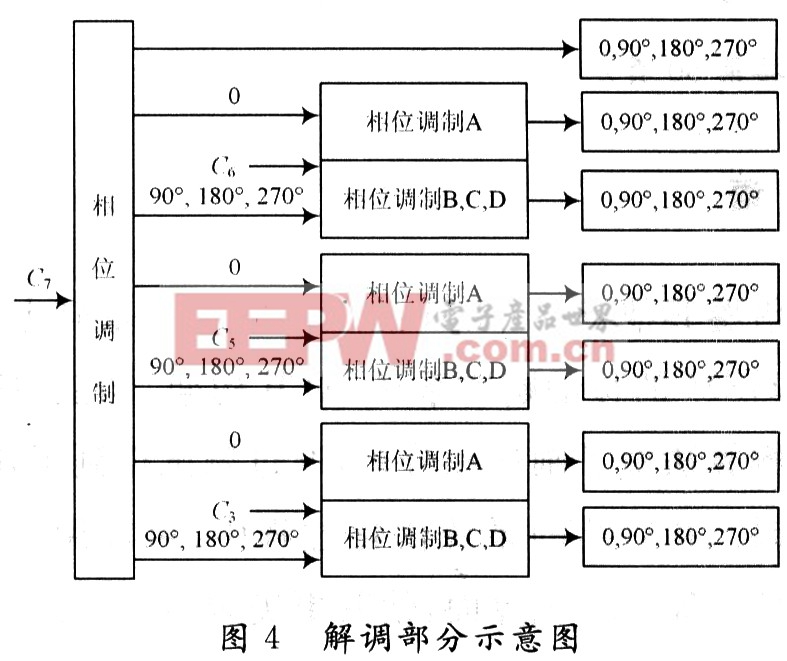

通過觀察式(7)可以看到,調制后的碼字C'={C0,C1,C2,C3,C4,C5,C6,C7},其中的C7與e-iθ1進行相關運算,根據最大峰值在相關結果中的位置,可確定θ1的值,也即解調出了φ1(φ1=θ1),然后再按照表1來確定d0,d1。碼字C中G是與一e“q。。吃’進行相關運算的,如果其中臼。的值已經確定,那么可以在島為定值的情況下,根據相關解調的方法,確定島的值;同理,G是與e’。∞t。如’進行相關運算的,G是與一e-“q也’進行相關運算的,可以通過類似C6的解調方法來確定夙,亂的值,由此也即知道了仰,仲,鉚的值(島一仇,晚一卿,亂一似),最后根據表2得到d。~d,的值。與其他的ccK解調方案相比,這種解調方案很好地簡化了計算過程,也減少了計算的工作量。圖4是解調部分的圖形表示。

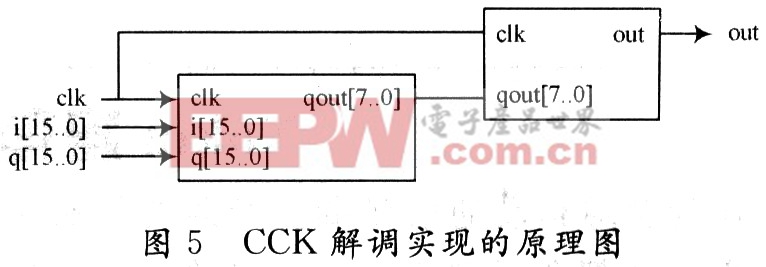

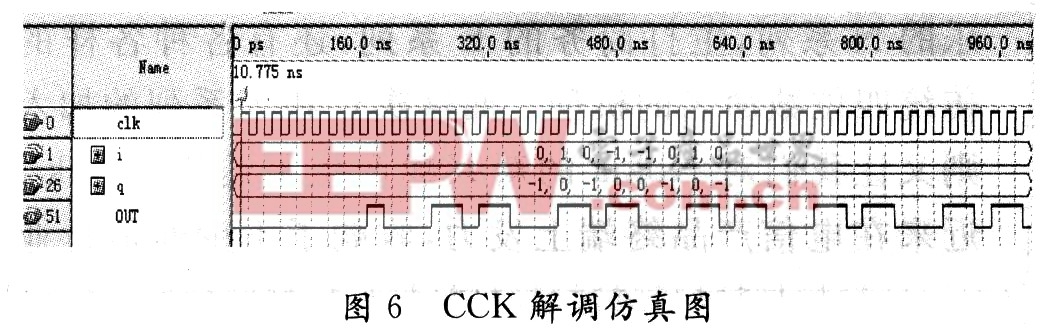

CCK解調實現的原理圖如圖5所示。這個模塊由ccK解調模塊和并串模塊兩大部分組成。

經過CCK解調,得到8位并行數據,再經由并/串轉換轉換成串行數據輸出。

3 結 語

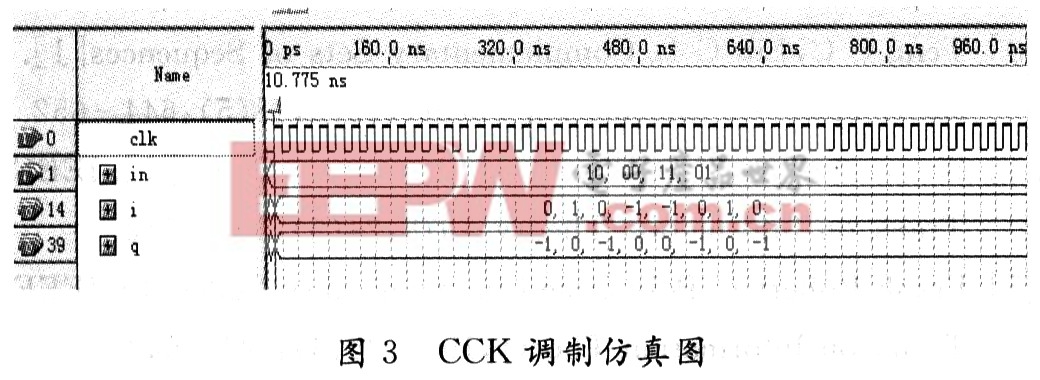

研究了補碼序列的定義和性質,并對CCK調制和解調原理進行了分析,提出了更為簡便、新穎的CCK調制解調方法,該方法降低了計算的復雜度,同時也大大減少了計算的工作量。本文還將該方法運用VerilogHDL硬件描述語言,通過QuartusⅡ7.2進行了功能仿真和時序仿真,同時還利用Altera公司最新的Cy-clone Ⅲ芯片EP3C25F324C8NES予以實現。CycloneⅢ前所未有地同時實現了低功耗、低成本和高性能。CycloneⅢ的系統最高頻率為505.05 MHz,I/O腳最高頻率為379.36 MHz,而類似型號的CycloneⅡ,Cyclone工的系統最高頻率分別為490.68 MHz和404.53 MHz,I/O腳最高頻率分別為91.76 MHz和204.25 MHz,CycloneⅢ的這一特性提高了系統的性能。同時該方案的實現只需用到97個邏輯單元,對CycloneⅢ總邏輯單元,其使用率為0.34%,而類似型號的CycloneⅡ,Cyclone I芯片的邏輯單元,其使用率分別為0.52%和0.48%。由此可見,這種全新方案節省了硬件資源,提高了CCK調制、解調的速率,簡化了計算過程,減少了計算量,同時Verilog HDL語言的運用,也增加了描述的靈活性和高效性。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論