基于FPGA和USB2.0的高速數據采集系統

2.3 接口電路

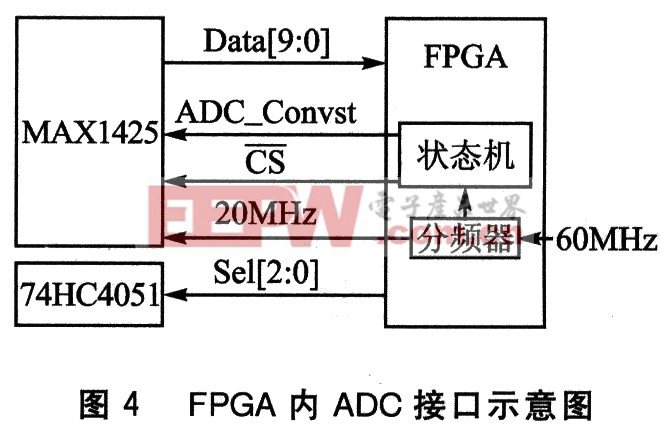

2.3.1 FPGA內的ADC接口模塊

MAX1425和74HC4051的控制信號都由FPGA產生,接口電路如圖4所示。本文引用地址:http://www.104case.com/article/188574.htm

FPGA的工作時鐘為60 MHz,該時鐘經過分頻后,提供20 MHz給MAX1425作為工作時鐘,同時也作為FP-GA內其他邏輯的工作時鐘。由FPGA內狀態機控制,當CS為低和ADC_Convst為高時,MAX1425進入采樣保持狀態。當Clock的第一個上升沿到來,MAX1425開始轉換。RD輸出為低時,MAX1425把轉換結果放到數據總線上,FPGA開始讀入10位數據(FD[15:0]中的10~15六位數據線懸空,使數據線和A/D的位數匹配)。FPGA控制寄存器的Sel[2:O]信號作為74Hc4051的通道選擇信號,從8路模擬輸入信號中選擇1路作為MAX1425的輸入。完成一次轉換后,當ADC_Convst:再次為高時,開始下一輪轉換。

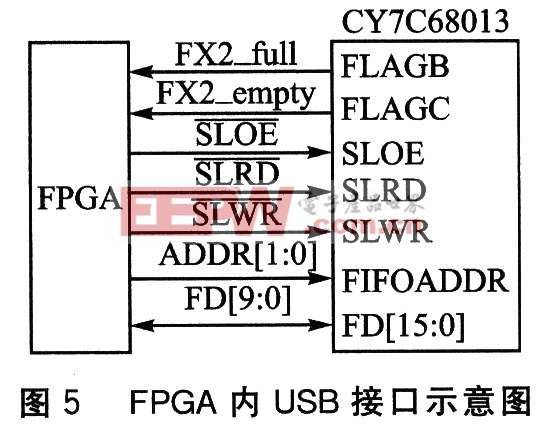

2.3.2 FPGA內的USB接口模塊

圖5是Slave模式下CY7C68013與FPGA的連接示意圖。中間是FPGA中USB接口模塊部分對應的信號。

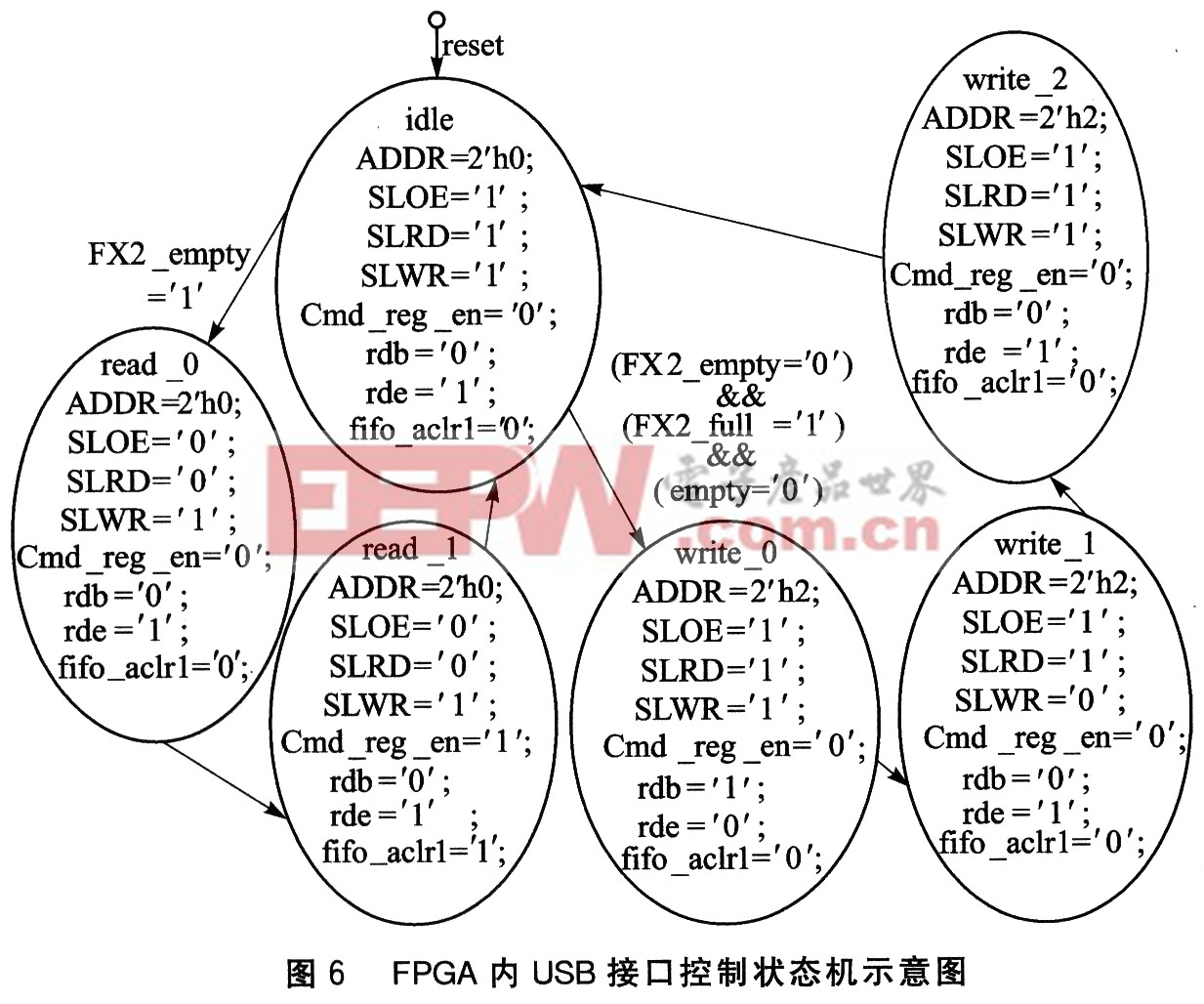

2.3.3 FPGA內的USB接口控制狀態機

FPGA內USB接口控制狀態機的狀態轉移圖如圖6所示。共有6個狀態,復位信號的模式設置為異步復位。狀態機主要分為讀、寫兩部分:讀取EP2中所包含的命令,存到FPGA的控制寄存器組中;將FPGA的FIFO中的數據讀出,寫入EP6端點緩沖區。

該狀態機工作過程為:

①系統加電或復位后,狀態機進入空閑狀態(idle)。

②在空閑狀態下,當EP2不為空時進入read_0狀態,從EP2中讀出PC機傳來的控制命令。隨后進入read_1狀態,把命令存到FPGA內控制寄存器中,并把FPGA內的FIFO清空(fifo_ach1='1'),以準備存儲采樣數據。之后再回到idle狀態。

③在空閑狀態下,當EP2為空(FX2_empty='0'),而FPGA的FIFO不為空(empty='0'),且EP6不滿時,進入write_0狀態。之所以要看EP2是否為空,是想優先處理PC機通過EP2傳來的命令。在write_0狀態下,選中對CY7C68013的EP6操作(ADDR=2'h2),同時從FPGA內部的FIFO中讀出一個數據。之后進入write_1狀態,把數據寫入CY7C68013。然后進入write_2狀態,write_2狀態的輸出與idle狀態相同,目的是提供一個時鐘周期的延遲。因為FPGA工作于60 MHz的時鐘下,比CY7C68013快,所以加入一個延遲以保證可靠的數據傳輸。

評論