基于四核DSP的視頻交通檢測系統設計

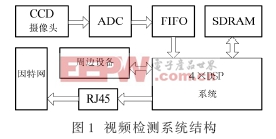

1視頻檢測系統整體方案

目前交通信息視頻檢測系統較為復雜,而且穩定性不高、價格昂貴、實時性不強,需要專人管理,操作較為繁瑣。本設計系統框圖如圖1所示采用4核DSP結構,通過4個系統單元間通信接口的連接,將4個數字信號處理器DSP相結合,體現了4微處理器系統的優勢。系統單元實現檢測算法并與外部設備交換數據。系統工作時,CCD攝像頭采集車流圖像信號經模數轉換得到數字視頻數據,數字視頻數據存入視頻緩沖器FIFO中,存滿一行后向4×DSP系統發出中斷請求信號;DSP中斷CPU,將數字視頻數據傳輸到內部存儲器SDRAM中,完成數字視頻圖像的采集和YUV變量分離,合成一幀完整的數字圖像數據;然后產生中斷通知算法處理程序對圖像進行處理,結果存儲在DSP地址空間約定好的緩沖區里,等待外部設備取走檢測結果,以作后續處理。

2 DSP簡介

DSP(數字信號處理器)自從1982年誕生以來,獲得了飛速的發展。本文采用4顆TI(Texas Instrument)公司高端DSP-TMS320C6416所設計,具有主頻高、雙套外部地址和數據總線等特點,非常適用于圖像處理等領域。有關該芯片的特點如下,詳細資料可見參考文獻[3]。

(1) DSP內核采用超長指令字(VLIW)體系結構,有8個功能單元、64個32 bit通用寄存器。一個時鐘周期同時執行8條指令,運算能力可達到 4800MIPS(每秒百萬條指令),支持8/16/32/64 bit的數據類型。兩個乘法累加單元一個時鐘周期可同時執行4組16×16 bit乘法或8 組8×8bit乘法,每個功能單元在硬件上都增加了附加功能,增強了指令集的正交性。除此之外還增加了一些指令用以削減代碼長度和增加寄存器的靈活性;

(2)為使數據能保持對超快速DSP內核的供給,TMS320C6416采用了兩級超高速緩存器,即16 KB的一級數據Cache、16 KB的一級程序Cache和1 024 KB的數據和程序統一內存。為了達到更大的擴展,1 024 KB內存中的256 KB存儲空間可設置用作二級Cache;

(3)TMS320C6416的存儲器接口提供了到SDRAM、SBSRAM、異步器件如SRAM/ROM等存儲器的無終端接口,也可連接到外部I/O器件;

(4)在TMS320C6416 中,增加了一個PCI接口,支持32bit寬的地址和數據復用總線,工作頻率最高為33MHz;

(5)DSP器件比通用CPU家族的動輒幾十瓦而言,其功耗一般在數瓦甚至毫瓦量級,這在各種功耗敏感場合顯示出獨特的優勢,同時省去了繁雜的散熱系統。本文采用C6416,I/O電壓為3.3 V,內核電壓為1.2 V。當時鐘頻率為600 MHz時,DSP的最大功耗小于1.6 W。

2.1 4×DSP的并行圖像處理系統

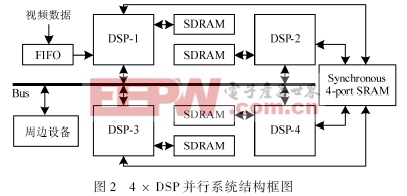

使用4個TI公司高端數字信號處理器TMS320C6416構建一種新型的并行圖像處理系統。該系統通過一個同步4口SRAM和系統總線構成互連結構,兼有緊耦合并行系統和松耦合并行系統的優點[4]。

2.2 4×DSP并行系統結構

圖像處理算法靈活多樣,而且還在不斷地迅速發展,為滿足日益復雜的圖像處理算法和逐漸變大的圖像規模,出于通用性考慮,系統中處理器之間需要靈活的、高帶寬的通信和握手機制。圖2給出了所設計的并行系統框圖,采用4顆TMS320C6416芯片,能較快完成以前一臺計算機需要長時間才能完成的任務。

從圖2可以看出,該系統以緊耦合系統和松耦合系統為基礎構架而設計的,結合了兩者的優點。緊耦合系統通過共享的存儲器來實現處理器之間的通信,處理器之間的聯系比較緊密。松耦合系統中每個處理器節點帶有存儲器[5],處理器之間通過消息傳遞的方式來相互通信。該系統每個節點即是一臺完整的DSP處理器并且帶有SDRAM存儲器,屬于松耦合系統;而所有節點共享一個同步4口SRAM存儲器,構成的整體是一個單一計算資源,屬于緊耦合系統。因此,該系統具有緊耦合系統和松耦合系統的優點,相比于前面兩者具有增強的可用性和更好的性能。

評論