基于FPGA的FIFO設計和應用

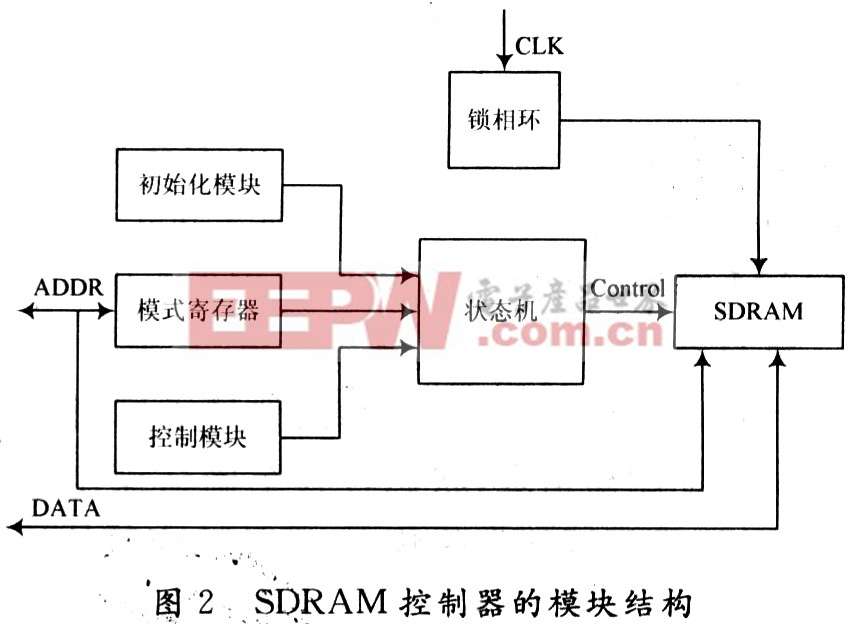

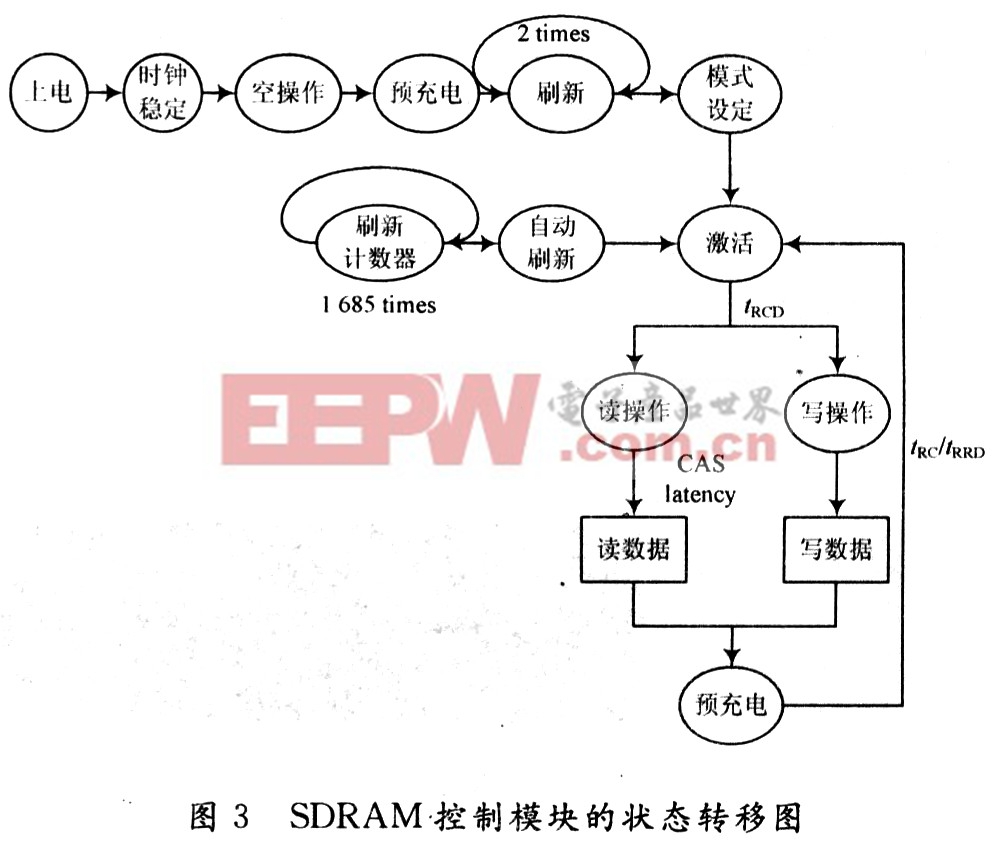

狀態機是SDRAM控制器的核心控制模塊,其作用主要有兩個方面:其一是對各模塊發出的操作請求進行仲裁,在適當的時刻作出反映,發出對SDRAM適當的控制命令;其二是協調各模塊之間的時序關系,滿足對SDRAM讀寫所必需的時序要求。狀態機的狀態轉移如圖3所示。

在模式設定之后,BANK和行地址選中需要訪問數據所在的具體BANK塊和行,狀態機對這一行發出激活命令,從激活到讀寫操作需要經過一個tRCD的延時,設計中選tRCD=20 ns,而系統時鐘周期為9.26 ns,所以從激活到執行讀寫操作之間至少需要3個時鐘周期。在執行讀寫操作時,只要狀態機通過讀寫命令選中數據所在行的列地址,就能達到讀寫具體存儲單元的目的。狀態機對SDRAM發出一個讀命令后,需要等待一個CAS latency,然后才能讀數據;而寫操作是實時的,不需要延時,狀態機在發出寫命令后,就可以對SDRAM進行寫操作。SDRAM同時只允許一行地址激活,因此在完成某BANK/ROW的讀寫操作后,對該BANK/ROW進行預充電,然后才能激活下一個BANK/ROW。從預充電成功到下一次激活命令成功,如果是在同一個BANK塊,則需要延時tRC,如果是不同的BANK塊,則需要延時tRRD。

SDRAM要求在64 ms之內對4 096行進行刷新,也就是每15.625μs刷新一行。由于系統時鐘周期為9.26 ns,所以刷新模塊計數達到1 685時,就需要對SDRAM發出刷新命令,保證SDRAM中的數據不丟失。將自動刷新請求設為優先請求,狀態機內部有請求仲裁邏輯,當自動刷新請求和其他請求同時出現時,優先保證自動刷新請求,狀態轉移至刷新操作,當刷新操作結束時,重新返回空閑狀態,開始響應其他請求。

3 工程應用介紹

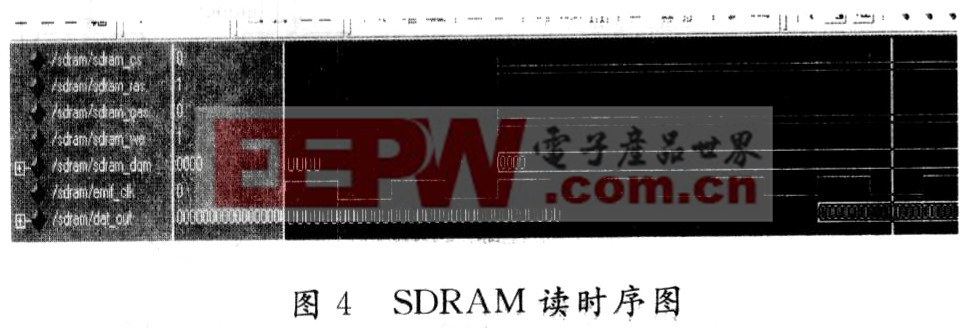

該設計目的是為了擴展TMS320DM642的FIFO容量,以FPGA為接口,實現與SDRAM的連接。TMS320DM642可以對4 GB的地址進行尋址,而實際應用中FIFO的容量只有256 KB,尋址空間為0x0184000~0x0187FFFF,因此在實際應用中必須進行擴展。這里采用1片MICRON公司的MT48LC4M3282型號的128 Mb SDRAM,采用32位數據總線,將其通過FPGA配置在TMS320DM642處理器的EMIFA CE3上,其地址范圍為0xB0000000~0xB7FFFFFF。在該設計中,突發長度為8,CAS latency為3。圖4為用Modelsim SE 6.0仿真的SDRAM讀時序圖。

4 結 語

該設計已應用于目標識別與跟蹤系統中的幀緩沖。文中主要介紹了SDRAM的具體信號關系,說明各種操作命令,給出在高速圖像存儲系統中SDRAM控制器的具體硬件接口設計。大容量存儲器是FIFO的發展方向,從現在通用的SDRAM、專用的SRAM,到DDR SDRAM,容量越來越大,速度也越來越快,而用FPGA作為SDRAM的控制器,具有最大的靈活性,也能在最大限度上發揮SDRAM高速度的優勢,因此對它進行研究具有重要的意義。

評論