一種高速實時數字波束形成器的設計

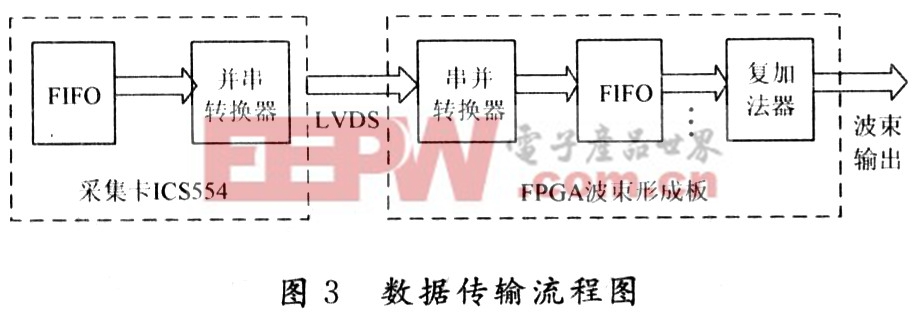

采集板ICS554本身給用戶預留有64個通用I/O口,可以將其配置為LVDS的I/O口,這樣可以提高數據傳輸能力和抗干擾性能。數據傳輸流程如圖3所示,ICS554內部FPGA先將24 b的I,Q數據流并/串轉換。VHDL語言的狀態機實現并/串轉換很容易,然后由LVDS發送模塊將LVTTL信號轉換成LVDS信號進行發送,接收端FPGA波束形成板首先將接收到的LVDS信號轉換成LVTTL信號,然后進行數據同步,再經過串/并轉換,將串碼恢復成24 b的I,Q數據。由于利用ICS554提供給用戶的通用I/O口配置為LVDS差分對,差分對的相位、互耦等都沒有很好的考慮,而且不能采用專用的平衡電纜連接,因而必須降低傳輸速率,以減小傳輸誤碼率,增強可靠性,同時考慮配置9位的LVDS口,8位并行傳輸數據,1位發送時鐘信號,LVDS傳輸速率為:

30×2×24/8=180 Mb/s

實際測試也表明,180 Mb/s的傳輸速度LVDS差分對能夠可靠的工作,FPGA波束形成板正確地接收到采集板ICS554的數據。本文引用地址:http://www.104case.com/article/188520.htm

2.2 實時波束形成計算

如前所述,整個實時波束形成分為兩次,首先在采集板ICS554中完成子陣波束形成,然后再到FPGA波束形成板中實現全陣的波束形成,如何保證整個計算的實時性是關鍵。

波束的形成,其實就是對A/D變換后數字信號進行幅度和相位加權,波束的特性如波束指向、副瓣電平、主瓣寬度等完全由權值決定。權值計算主要考慮兩方面的因素,首先要對各通道進行幅相校準,克服各通道不一致和互耦的影響,然后實現空域濾波,完成希望的波束指向。首先幅相校準,對于第i單元:

式中:δφi,△ai分別為第i通道與標準通道的相位差和幅度比值。若要實現空域濾波則需要在此基礎上增加陣因子對幅度和相位加權。

![]()

式中:φi為第i通道相位加權值;αi為幅度加權值,可以根據不同的波束性能要求(主瓣寬度、旁瓣電平、零陷位置)靈活選擇不同的幅度加權形式,得到不同的αi,權值矩陣W也會有所不同。權值更新計算由DSP處理板完成。

最初的子陣波束形成需實現四通道單元的波束形成,即對4路中頻數字I,Q兩路信號復加權求和:

式中:Iout,Qout為4通道波束形成后I,Q兩路輸出結果;ωir,ωii分別為第i單元權值的實部、虛部。由于ICS554采樣頻率比較高,而FPGA片內剩余可利用的資源比較多,在這里采用并行復乘運算,運用ISE軟件IP核設計映射出4個獨立的復乘運算單元,片內VHDL程序設計如圖4所示。

用4塊采集板ICS554獨立進行子陣波束形成,然后將結果Iout,Qout輸出給FPGA波束形成板進行復求和,最終得到16個天線單元的全陣合成波束。考慮FPGA運算的復雜性,選用內含DSP內核的Xilinx公司的XC3SD3400A芯片,該芯片性價比非常高,內含的DSP內核XtremeDSP DSP48A運算速度可以達到250 MHz,差分I/O傳輸速率可達到622 Mb/s。要保證整個波束形成運算的實時性,主要從采集板子陣波束形成運算、數據傳輸、FPGA板全陣波束形成運算三個方面測試分析。全陣波束形成運算主要是在XC3SD3400A內做復數加法運算,加法運算最高可以到250 MHz,遠遠高于數字下變頻后數據流速度。子陣波束形成運算則是在XC2V1000內做四通道并行復乘運算和復加運算,片內復乘流水線、復加運算時鐘頻率可達420 MHz。實際上,子陣和全陣波束形成的運算能力都是足夠的,整個系統的主要瓶頸還是數據傳輸,數據傳輸流量大,數據傳輸I/O口位寬達8位,在數據傳輸環節,將低速多位并行數據用倍頻時鐘轉換成250 MHz高速串行數據;在接收端,使用移位寄存器實現串/并轉換就可以得到低速并行數據。仿真和實際測試也表明,能夠保證整個系統波束形成運算的實時性。

3 結 語

這里設計的高速實時波束形成器,改善了原DBF系統,不僅可完成測向工作,同時實現了高速數據傳輸和全陣的實時數字波束形成。系統是基于采集板ICS554搭建的,ICS554雖然是一款高性能的4通道采集板,但是它成本高,而且只提供PCI接口,沒有提供其他高性能的數據傳輸接口,當陣元數更多時其可擴展性并不強。為了達到數據傳輸能力的要求,采用了多組LVDS差分對數據進行傳輸,雖然實現了要求的速度,但是連接電纜太多,互耦影響大、傳輸距離短。因而,后續的系統設計中,利用FPGA集成速度更快的高速串行差分RocketIO通道、光纖傳輸等技術來改善性能,提高系統可擴展性。

評論