基于HyperLynx的高速PECL交流耦合時鐘

引言

本文引用地址:http://www.104case.com/article/188363.htm隨著電子技術的不斷發展,數據的傳輸速度越來越快,高速時鐘的應用日益廣泛,如何保證時鐘在高速跳變過程中的信號完整性、抖動、功耗等問題,已逐漸成為關注的問題。傳統的時鐘設計方法大多依靠經驗和理論計算,但是隨著時鐘頻率越來越高,時鐘的電磁環境日趨復雜,時鐘的傳輸線效應、過沖/欠沖、反射、振鈴效應、趨膚效應都成為影響時鐘設計的關鍵因素,只有使用現代科技手段,利用計算機的強大計算能力進行仿真才能夠保證時鐘電路設計成功。 HyperLynx是Mentor(Graphics開發的一款板級信號完整性的仿真工具。它可以進行損耗傳輸線的精確仿真,支持IBIS模型和HSPICE模型,可以使用過孔模型,允許多種激勵源,可以分析信號的眼圖、抖動以及EMC(電磁兼容性)輻射,用戶界面簡單直觀。

在目前的高速時鐘的電平標準中,PECL(正電壓射極耦合邏輯)是應用較廣泛的一種,絕大多數高速ADC(A/D轉換器)、DAc(D/A轉換器)器件都支持這一時鐘電平。本文敘述。PECL的原理和常見端接方式,結合在ADc系統中的應用,使用HyperLynx工具對設計后的電路進行仿真以驗證設計思想。

l PECL工作原理

PECL由EcL(射極耦合邏輯)標準發展而來,在PECL電路中省去了負電源,較EcL電路更便于使用。PECL信號的擺幅相對EcL要小,這使得該邏輯更適合于高速數據的串行或并行連接。

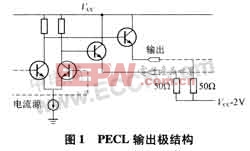

一個標準的PECL輸出極如圖1所示。

|

差分對管的射極通過電流源連接到地,差分對管驅動一對射隨器以提供正、負輸出。輸出射隨器工作在正電源范圍內,其電流始終存在,這樣有利于提高開關速度。LVPECL(低電壓。PECL)輸出極的標準輸出負載是接50 Ω電阻至Vcc一2 V的電平,在這種負載條件下,由于射隨器的基極一射極有0.7 V壓降,故輸出+與輸出一的靜態電平典型值為Vcc一1.3 V,0.7 V壓降加在50 Ω終端電阻上的電流為14 mA,可知輸出+與輸出一電流為14 mA。PECL結構的輸出阻抗典型值為4 Ω~5 Ω,表明它有很強的驅動能力。2時鐘電路設計

下面根據具體應用進行設計。首先從時鐘的發送端(輸出)和接收端(輸入)各自的特性著手進行設計。

2.1時鐘輸出結構

時鐘輸出端由時鐘扇出芯片ICS853011的一對輸出引腳擔任。ICS853011是一款將任意差分時鐘扇出為兩路PEcL電平的時鐘扇出芯片,其原理見圖2。

|

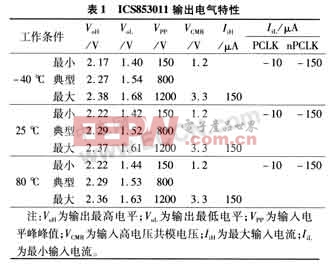

當其供電電壓為3.3 V時,其輸出電氣特性如表l所示,輸出高電平在2.295 V左右,輸出低電平在1.52 V左右,輸出峰峰值約為800 mV。

|

評論