高速數字記錄系統中光纖下載卡的邏輯設計

所用Xilinx的RocketIO核其實為aurora 核,這是一個雙向串行數據通信鏈路控制器,能將反壓信號隨數據一起發往對端。其接口相對簡單,有兩種模式,一種是幀模式,另一種是流模式,可以根據應用靈活選擇。在本項目中采用的是幀模式。

主DMA處理的軟硬件流程

在DMA處理中,采用內存乒乓操作來提高系統的吞吐量。軟件中的驅動采用Windriver開發,其工作主要分三部分。

1 初始化,包括申請內存,配置DMA列表,配置DMA相關寄存器,啟動邏輯開始工作。

2 中斷處理函數。在此函數中,屏蔽中斷,并啟動DPC處理。

3 DPC(延遲過程調用),根據邏輯提供的狀態標識,將相應的內存塊的數據搬移至硬盤中,然后取消中斷屏蔽,復位狀態標識,使系統可以接收下一個中斷。

數據的搬移不在中斷處理函數中完成,是由于中斷處理函數具有較高的優先級,如果將耗時的數據搬移放在這里進行,會明顯降低系統的響應時間。而DPC的優先級在所有的外部中斷之下,不會因此而降低對其他外部中斷的響應速度。

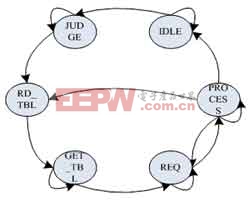

主DMA邏輯的主要工作是讀取驅動配置的DMA列表,根據列表中的內存地址和長度,對內存進行主DMA寫操作。操作完成后,通過置位狀態標識,通知驅動來讀取數據。狀態機轉移如圖4所示。

圖4 DMA主狀態機轉移圖

● IDLE狀態:在此狀態下,等待軟件的使能信號。使能信號有效則進入JUDGE狀態,否則等待。

● JUDGE狀態:在此狀態下,判斷乒乓標志。根據乒乓標志決定本次處理應該選擇哪一個內存塊。

● RD_TBL狀態: 發出讀DMA列表的地址信息。然后進行GET_TBL狀態接收列表數據。

● GET_TBL狀態:在此狀態下,讀取DMA列表數據,并將列表中的內存地址和長度信息寫入相應的寄存器中。然后進入REQ狀態。

● REQ狀態:在此狀態下,對異步FIFO的空信號進行判斷。如果非空,則進入PROCESS狀態,否則在REQ狀態等待。

● PROCESS狀態:在此狀態下,進行數據傳輸。由于PCI主DMA對burst長度有限制,當傳輸完預定長度的數據后,首先對本次長度進行判斷。如果未完則進入REQ狀態等待,否則判斷本列表是否最后一個列表。如果是,則進行IDLE狀態。否則進入RD_TBL狀態讀取下一條DMA列表表項的數據,繼續處理。

評論