高速數字記錄系統中光纖下載卡的邏輯設計

中斷控制方式是外圍設備收到數據后,向CPU發送中斷。CPU收到中斷后,再控制數據在其內存和外圍設備之間的傳輸。它的優點是大大提高了CPU的利用率且能支持多道程序和設備的并行操作。它的缺點是由于數據緩沖寄存器比較小,如果中斷次數較多,仍然會占用大量CPU時間。在外圍設備較多時,由于中斷次數的急劇增加,可能造成CPU無法響應中斷而出現中斷丟失的現象。如果外圍設備速度比較快,可能會出現CPU來不及從數據緩沖寄存器中取走數據而丟失數據的情況。本文引用地址:http://www.104case.com/article/188359.htm

DMA方式是在外圍設備和內存之間開辟直接的數據交換通路進行數據傳送。外圍設備通過通用總線直接訪問內存,將其收到的數據寫入內存或將要發送的數據讀出內存。上述操作完成后,再通過中斷的方式通知CPU,由CPU進行后繼的處理。它的優點是除了在數據塊傳送開始時需要CPU的啟動指令,在整個數據塊傳送結束時需要發中斷通知CPU進行中斷處理之外,不需要CPU的干涉。

可見,下載設備和微機之間通過主DMA方式進行通信,可以大大的提高數據傳輸速率。66MHz/64位寬的PCI總線在理想情況下可以提供近500Mb/s的傳輸速率,可以比較容易的達到250Mb/s的光纖下載速度,所以下載的瓶頸在于硬盤的讀寫速度。普通硬盤的平均讀寫速度在60Mb/s,采用4個盤一組的陣列盤,差不多可以達到60×4=240Mb/s的速度。

由上述數據可以看出,采用64位的PCI總線,用主DMA方式進行數據傳輸,下載的最大速度將大于200Mb/s。

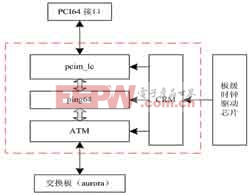

FPGA邏輯內部結構

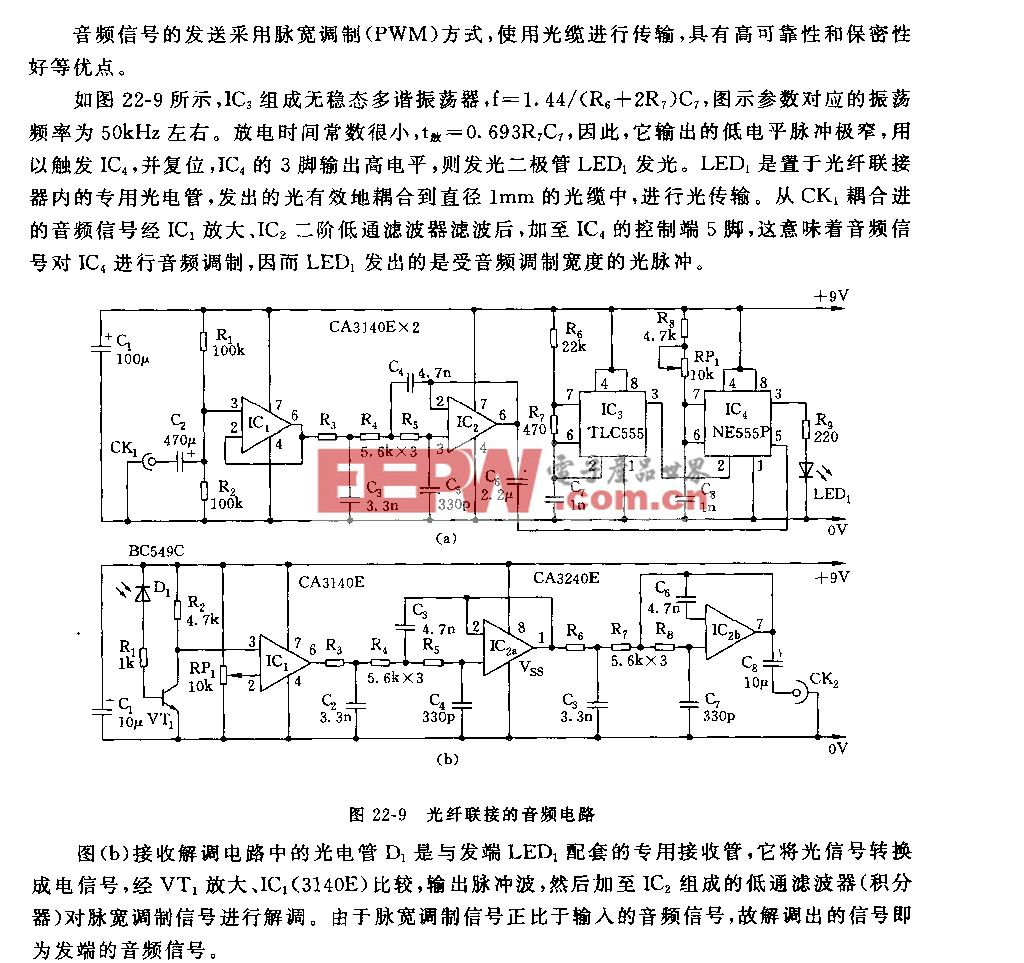

邏輯總體結構圖如圖3所示,數據流方向為:串行的光纖數據首先進入ATM(Aurora Transmit Module)模塊,由ATM模塊內部的Xilinx RocketIo核將串行數據轉換成并行32位數據。并行數據經過FIFO進行緩存后,進入PING64模塊。Pin64模塊內部邏輯產生主DMA時序,并將FIFO數據送上內部總線。Pcim_lc將內部總線信號轉換成PCI總線信號并送出去。各個模塊的功能具體如下。

圖3 FPGA內部結構圖

● Pcim_lc模塊為Xilinx提供的PCI64位的軟核;

● Ping64模塊包括和PCI64軟核的接口以及主DMA處理邏輯;

● ATM為和光纖輸入的接口模塊,采用Xilinx提高的Aurora協議對數據進行控制,ATM只需提高用戶邏輯和Aurora的接口即可;

● CRM為時鐘和復位信號產生模塊。

評論