高速流水線浮點加法器的FPGA實現

3.2浮點加法運算的實現

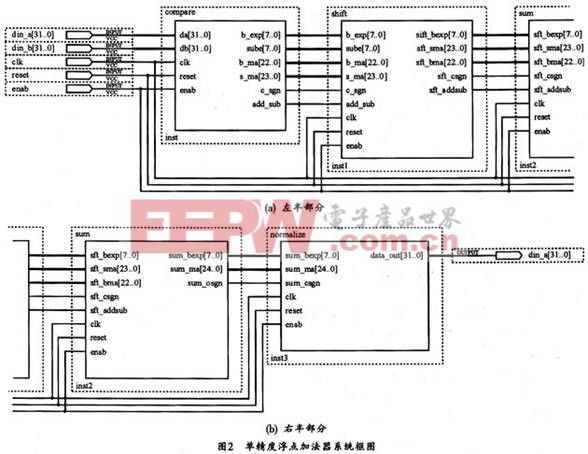

浮點加法運算可總結為比較、移位、相加、規范化等四個步驟,分別對應于compare、shift、sum、normalize四個模塊。

(1)compare模塊

本模塊主要完成兩輸入浮點數的比較,若din_a、din_b為兩個輸入單精度浮點數,則在一個時鐘周期內完成的運算結果如下:

◇大數指數b_exp這里的大數指絕對值的比較;

◇兩浮點數的指數差sube,正數;

◇大數尾數b_ma;

◇小數尾數s_ma,該尾數已加入隱含1;

◇和符號c_sgn,為確定輸出結果的符號;

◇加減選擇add_sub,兩輸入同符號時為0(相加)、異符號時為1(相減),sum模塊中使用實現加減選擇。

(2)shift模塊

shift模塊的作用主要是根據兩個輸入浮點數的指數差來執行小數尾數(已加入隱含1)向右移動相應的位數,以將輸入的兩個浮點數指數調整為相同的數(同大數),若b_exp、sube、b_ma、s_ma、c_sgn、add_sub為輸入信號(其含義見compare模塊),則可輸出如下運算結果(在一個時鐘周期內完成):

◇大數指數(sft_bexp),將b_exp信號用寄存器延遲一個周期,以實現時序同步;

◇小數尾數(sft_sma),已完成向右移動相應的sube位;

◇大數尾數(sft_bma),將b_ma信號用寄存器延遲一個周期,以實現時序同步;

◇和符號(sft_csgn),將c_sgn信號用寄存器延遲一個周期,以實現時序同步;

◇加減選擇(sft_addsub),將add_sub信號用寄存器延遲一個周期,以實現時序同步;

(3)sum模塊

本模塊可根據加減選擇(sft_addsub(信號完成兩輸入浮點數尾數(已加入隱含1)的加減,若sft_bexp、sft_sma、sft_bma、sft_csgn、sft_addsub為輸入信號(其含義見shift模塊),則可輸出如下運算結果(在一個時鐘周期內完成):

◇大數指數(sum_bexp),將sft_bexp信號用寄存器延遲一個周期,以實現時序同步;

◇尾數和(sum_ma),為大數尾數與移位后小數尾數的和,差(兩尾數已加入隱含1);

◇和符號(sum_csgn),將sft_csgn信號用寄存器延遲一個周期,以實現時序同步;

(4)normalize模塊

評論