SignalTapII ELA的FPGA在線調試技術

完成STP配置,將sof文件配置到FPGA,運行SignalTapII ELA,當待測信號條件滿足時,數據捕獲開始,捕獲的數據以波形的形式表示出來。SignalTapII ELA也可將捕獲數據通過多余的I/O引腳輸出,以供外部的測試設備使用。

3 實例分析

本文以一個基于DDR SDRAM高速數據采集IP核的設計為例,具體說明如何用SignalTapII ELA來進行FPGA在線調試。使用Altera公司的器件CyclonelI系列FPGA EP2C5F256C6,該器件支持SignalTap II ELA。

當前需要測試來自3個模塊的信號:外部存儲器DDR SDRAM與FPGA的接口信號、FPGA內部輸入輸出PIO寄存器信號、FPGA內部RAM接口信號。

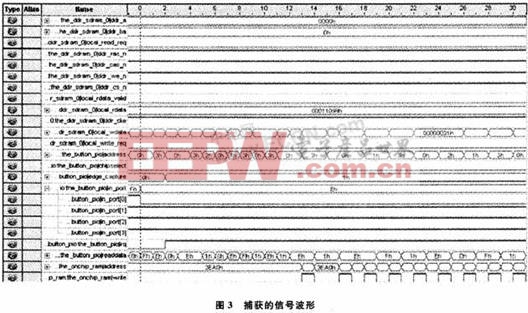

先關閉增量編譯,設置采樣時鐘為外部獨立時鐘CLK=50 MHz;采樣深度為256;RAM類型為M4K,數據寬度分割為256×1;觸發位置為Pre trigger position;觸發信號為DDR SDRAM讀操作信號;觸發條件為Basic單信號觸發;觸發條件級數為1級。從圖2可知,該觸發信號設置為上升沿觸發有效。重新編譯后將包含SignalTapIIELA的sof配置文件下載到FPGA中,圖3即是從SignalTap II ELA數據窗觀察到的來自FPGA內部實時信號的捕獲波形。

如果設計文件中添加SignalTapII ELA后編譯時間顯著增加,可以考慮使用Start AnalysisElaboration代替Start AnalysisSynthesis,這樣可以顯著縮短編譯時間。

加入SignalTapII ELA后,如果發現一些用于調試的邏輯(比如調試用的計數器)被優化掉,不能出現在波形中,可以嘗試這樣解決:在HDL設計文件中對要調試的信號添加保持或保護屬性。

保持屬性主要用于信號和網絡節點。代碼如下(以VHDL為例):

signal my_signal:bit;

attribute syn_keep:boolean;

attribute syn_keep of my_signal signal is true;

保護屬性主要用于寄存器。代碼如下(以VHDL為例):

signal my_reg:std_logic;

attribute preserve:boolean;

attribute preserve of my_signal:signal is true;

通過改變待測信號的觸發方式和條件,可以捕獲到其他相類似的信號波形,這里就不一一列舉。

需要注意的是,SignalTapII ELA本身是一塊獨立邏輯資源,需要占據FPGA資源。比如RAM、LE等,資源消耗量與需采集的數據量成正比,采集存儲的數據深度由設計中的內部RAM剩余大小決定。在調試完成后,需將SignalTapII ELA從系統邏輯設計中移除,以免浪費資源和影響設計的性能。

結 語

通過對FPGA內部信號的捕獲測試,可以實現對系統設計缺陷的實時分析和修正。與外部測試設備相比,可以總結出SignalTapII ELA的幾點優越性:不占用額外的I/O引腳,不占用PCB上的空間,不破壞信號的時序和完整性,不需額外費用;從多方面證實,該測試手段可以減少調試時間,縮短設計周期。

評論