J-FET開關電路工作原理

1、簡單開關控制電路

本文引用地址:http://www.104case.com/article/187981.htm圖5.4-97為簡單J-FET開關電路。當控制電壓VC高于輸入電壓V1時,VGS=0,J-FET導通,傳輸信號至VO;當VC比V1足夠負,VD導通而J-FET截止,VO=0。

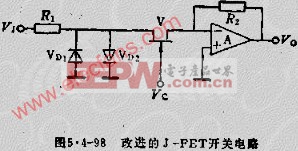

2、改進的J-FET開關電路

圖5.4-98電路是圖5.4-97電路的改進,增加一級運算放大器以克服J-FET內阻較大的缺點。電路中R1使J-FET上的壓降較小,即VD≈VS=0。當VC=0時J-FET導通而與V1大小無關;當VC比夾斷電壓稍負時,J-FET截止,由于VD1或VD2導通,漏極電位被鉗在±0.6V。R1的阻值視V1的幅值選定。運算放大器將傳輸信號倒相。

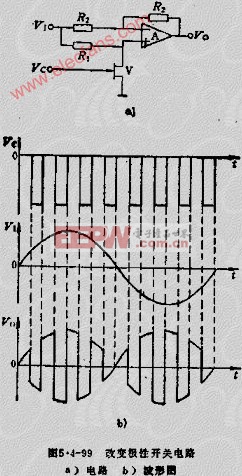

3、改變極性的J-FET開關電路

圖5.4-99A所示電路為可改變極性的放大電路。電路應使R1遠大于J-FET導通電阻而遠小于J-FET的截止電阻,即RONR1ROFF(對漏和源而言)。當VC=0時,J-FET導通,電路為反相跟隨器,VO=-V1;當VC比V1最低幅度還低時,J-FET截止,R1上無電流,運算放大器同相輸入端電位FIN+=V1,由于反饋,反相輸入端電位VIN-=V1,R3上亦無電流,則V0=V1。R1不一定與R1相等或匹配,如果運算放大器輸入阻抗很高,R1可選大些。圖5.4-99B示出了一種通過該電路的信號波形。

評論