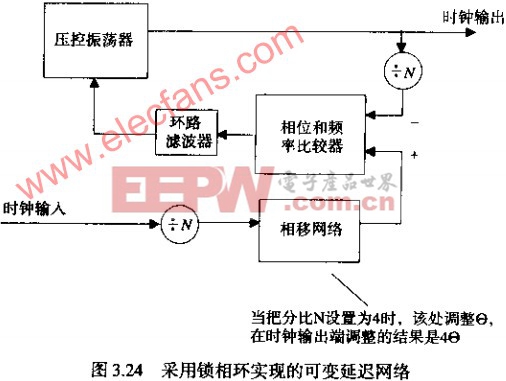

采用鎖相環(huán)的時(shí)間調(diào)整

圖3.24給出了CADILLAC時(shí)鐘相位調(diào)整電路的框圖。對(duì)于大規(guī)模生產(chǎn)測(cè)試,可能值得構(gòu)造這樣的電路。對(duì)于普通的實(shí)驗(yàn)測(cè)試,則太麻煩了。

本文引用地址:http://www.104case.com/article/187915.htm

電路將總線時(shí)鐘進(jìn)行N分頻,然后通過一個(gè)-頻率比較器把它與一個(gè)同樣經(jīng)過N分頻的本地振蕩器相比較。電路的頻率鎖定在與總線時(shí)鐘相同的頻率上,但是相位由相移網(wǎng)絡(luò)決定。

因?yàn)橄辔绘i定的頻率是時(shí)鐘振蕩器頻率的I/N,因此如果在相移網(wǎng)絡(luò)中加入Y度的相移調(diào)產(chǎn)生一個(gè)很小的相移。由變?nèi)荻O管控制的RC移相器可以很方便地做到這一點(diǎn)。

這個(gè)電路的相位調(diào)整范圍可以超過正負(fù)180度。當(dāng)系統(tǒng)的時(shí)鐘較高,并且經(jīng)過分頻將信號(hào)頻率降低來產(chǎn)生本地控制信號(hào)時(shí),這種較大的相位調(diào)整非常有用。大的相位調(diào)整對(duì)調(diào)試允許多個(gè)時(shí)鐘周期抖動(dòng)的導(dǎo)步電路也很有用,例如通信中的T3同步器和FIFO電路等。

VCO的穩(wěn)定性和相位檢測(cè)網(wǎng)絡(luò)的噪聲不敏感特性,在這個(gè)電路里面至關(guān)重要。如果并不擅長(zhǎng)模擬電路的設(shè)計(jì),最好在制作這個(gè)電路時(shí)尋求些幫助。

評(píng)論