NxN MIMO基站與外部時序參考同步

同步的一個重要結果就是“保持”的概念。如果時序參考丟失(例如,建筑物在每天的某一時間段擋住GPS衛星信號),參考時鐘必須保持與存在時序參考情況下一樣的狀態。ANSI/T1.101-19873等標準將保持要求劃分為多種層次,每種層次均規定了特定時間內允許的不同最大偏移。Stratum 3E是Bellcore GR-1244-CORE4所定義的一個附加層次,它要求時鐘源在24小時內的偏移量不得超過億分之一。

正如下面的N×N MIMO系統部分所述,如果一個基站在多輸入多輸出架構中使用兩個或更多收發器,該基站必須使所有收發器與同一時序參考同步。為了降低器件數量及成本,參考時鐘應能夠提供多個完全相同的輸出,每個輸出都能驅動不同的收發器模塊。

案例研究:提供外部時鐘

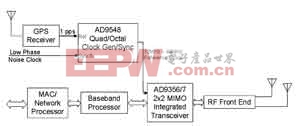

本案例研究使用AD9356/7 2×2 MIMO集成收發器作為基站系統的組成部分。如前所述,AD9356/7要求32~48MHz的參考時鐘頻率。要將此時鐘與時序參考同步,需使用具有出色相位噪聲性能的靈活PLL,像ADI公司的4/8通道輸入網絡時鐘發生器/同步器AD9548完全符合這一要求。時序參考輸出連接到AD9548的一路參考輸入,一個低相位噪聲時鐘連接到系統時鐘輸入。輸出設置為AD9356/7所需的32~48MHz參考時鐘。圖2顯示了一個GPS同步系統的框圖。

圖2 采用GPS參考的基站架構

一些網絡時鐘發生器可以支持極寬的輸入頻率范圍,從而提供各種不同的時序參考和低相位噪聲時鐘。明智選擇輸入頻率可以簡化設計,降低成本,實現最佳的發射和接收性能,并達到保持性能要求。

AD9548利用數字鎖相環(DPLL)將輸出時鐘鎖定至時序參考,而不是模擬PLL。這種技術可使系統實現極佳的保持性能,只受系統時鐘源的時序漂移限制。此外,決定AD9548輸出時鐘相位噪聲性能的因素是系統時鐘的相位噪聲,而不是時序參考,因此該器件可以接受高噪聲時序參考,而不會將此噪聲傳遞至其輸出。

實現最高參考時鐘性能

網絡時鐘發生器支持寬范圍的輸入和輸出頻率,從而為系統架構師優化輸出時鐘性能提供了許多選擇。

例如,25MHz及以下頻率的高穩定性時鐘源相對更豐富,而且比更高頻率時鐘源便宜。如果圖2所示的系統時鐘(sysclk)輸入小于50MHz,則可利用AD9548中的倍頻器使系統時鐘加倍,由此增加的相位噪聲極小。然后利用這一更高頻率,系統時鐘PLL可將時鐘提高到約1GHz。

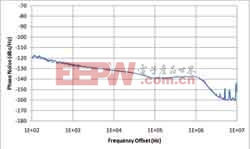

設計師還必須選擇DPLL輸出頻率及由此產生的后置分頻器比率。DPLL輸出頻率越高,則壓擺率越快,一般有助于降低相位噪聲,但也可能導致雜散折回頻譜中。對于AD9356/7參考時鐘,一個有效的折中選擇是將DPLL輸出頻率設為240MHz,并將后置分頻比設為6,得到40MHz的最終輸出頻率。圖3顯示了AD9548在這些設置下的相位噪聲。

圖3 ADI公司AD9548相位噪聲與頻率的關系

圖4顯示利用AD9548提供參考時鐘,并以2500MHz進行傳輸時AD9356輸出端的積分相位噪聲。AD9548評估板可以利用其自有片內系統時鐘XO(出廠配置)或外部時鐘。圖3和圖4所示為AD9548使用一個12.8MHz恒溫控制晶振(OCXO)作為其系統時鐘輸入的情況。此測試中,AD9548未與時序參考同步。

評論