NxN MIMO基站與外部時序參考同步

針對電信基站,系統(tǒng)架構師需要花費相當多的精力和時間設計高性能時鐘和正弦波振蕩電路。單芯片收發(fā)器雖然整合了許多此類信號發(fā)生器,但仍然需要一個參考時鐘。一個網(wǎng)絡中的各基站一般相互同步,因此該參考時鐘必須與一個全網(wǎng)絡時序信號保持時序一致。本文討論一個高性能時鐘發(fā)生器如何配合一個或多個集成收發(fā)器工作,以便簡化整體設計、降低復雜度和成本,同時實現(xiàn)出色的系統(tǒng)接收和發(fā)射性能。即使基站長時間丟失時序參考信號,網(wǎng)絡中的所有其他基站仍能保持同步。

本文引用地址:http://www.104case.com/article/187888.htm基站時鐘架構

最常提到的一個基站參數(shù)是其載波(或本振)頻率。產(chǎn)生本振的頻率合成器是基站的重要組成部分,但正如所有系統(tǒng)設計師都知道的那樣,本振只是基站需要的多個內(nèi)部頻率中的一個。單就收發(fā)器而言,除了向混頻器級提供載波頻率的本振(LO)以外,數(shù)據(jù)轉(zhuǎn)換器需要采樣時鐘,數(shù)字濾波器需要時鐘,I/O總線則通常需要數(shù)據(jù)時鐘。

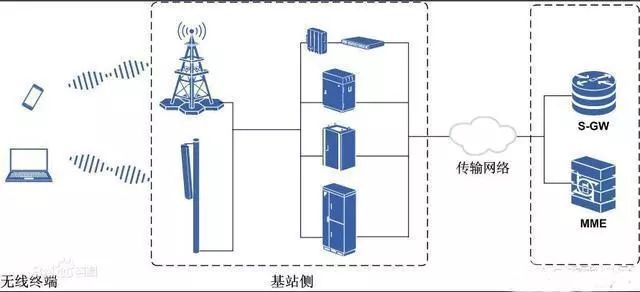

使用集成收發(fā)器,系統(tǒng)架構師可以節(jié)省大量設計時間和成本,如圖1中的虛線框所示。除了接收器和發(fā)射器電路以外,單芯片收發(fā)器還集成鎖相環(huán)(PLL),以產(chǎn)生各種信號處理模塊所需的時鐘和正弦信號。不過,再高集成度的收發(fā)器也需要參考時鐘輸入。

諸如ADI公司AD9356和AD9357之類的單芯片2×2多輸入/多輸出(MIMO)收發(fā)器,提供兩種不同的參考時鐘選項。一種是將一個外部晶振配合片內(nèi)數(shù)字控制調(diào)整電路(DCXO)使用,另一種是為器件提供一個外部時鐘。AD9356/7接受32~48MHz范圍內(nèi)的參考時鐘頻率。

用戶端設備(CPE)等用戶站使用基站所發(fā)送的信息與無線網(wǎng)絡同步。CPE設備會微調(diào)其本振頻率,同時也會與基站主時鐘保持時間同步。因此,上述外部晶振加DXCO選項是針對此應用的一種低成本、高性能解決方案。

基站會有其他要求。例如,運營商通常要求特定網(wǎng)絡內(nèi)所有站點的幀和符號邊界保持時序一致。由于基站負責向其相關用戶站提供時序信息,因此這一要求意味著網(wǎng)絡內(nèi)的所有基站必須鎖定至一個外部時序參考。系統(tǒng)架構師使基站同步的方法一般有兩種。一種方法是使用GPS接收機所提供的1pps(脈沖/秒)輸出,另一種方法則使用IEEE 1588標準所規(guī)定的網(wǎng)絡時序協(xié)議。無論何種情況,圖1所示的收發(fā)器參考時鐘輸入均與時序參考(例如,1pps GPS時鐘)同步。

基站參考時鐘設計考慮

如圖1所示,集成收發(fā)器將參考時鐘用作PLL的輸入。如果是RF PLL,基站會將參考時鐘倍乘至最高為LO頻率。此乘法系數(shù)可以是8或更大。因此,為使收發(fā)器實現(xiàn)高性能,參考時鐘的相位噪聲必須非常低。

圖1 2x2 MIMO基站收發(fā)器架構

評論