開關(guān)電源EMI濾波器設(shè)計(jì)

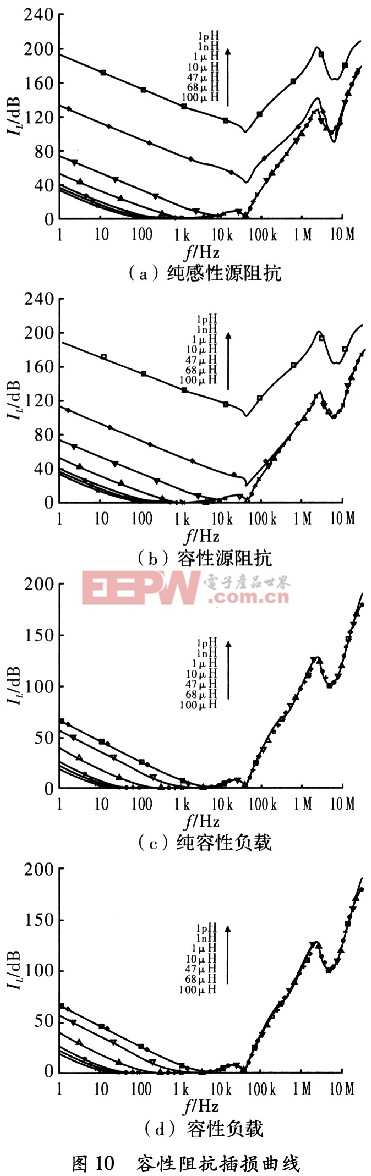

2.3.3 容性阻抗對插損的影響

圖10(a)中源阻抗為純?nèi)菪?不考慮寄生參數(shù)),電容越小,整體插損越大,尤其在μF~nF量級,nF~pF量級范圍插損低頻段增加很快,電容增加到mF量級后,電容變化幾乎對插損沒有影響。圖10(b)源阻抗為容性(考慮寄生參數(shù)),電容越小,整體插損越大,相比純?nèi)菪栽醋杩蛊湓趎F量級插損較小,整體上電容的高頻寄生參數(shù)對插損影響較小。圖10(c)中負(fù)載為純?nèi)菪?不考慮寄生參數(shù)),隨著電容值逐步增大,其在工頻附近插損越來越小,對有用信號的衰減變小,但在高頻范圍負(fù)載電容變化對插損幾乎沒有影響。圖10(d)中負(fù)載為容性(考慮寄生參數(shù)),隨著電容值逐步增大,其在工頻附近插損越來越小,相比圖10(c)說明電容高頻寄生參數(shù)對插損影響很小。比較圖8~圖10,源阻抗特性在頻段1 Hz~30 MHz整個(gè)對插損影響很大,而負(fù)載阻抗特性只在1 Hzf39.8 kHz頻段對插損有影響,其在39.8 kHzf30 MHz頻段插損不隨負(fù)載變化。電感的寄生參數(shù)對插損影響大,電容的寄生參數(shù)對插損影響較小。容性阻抗無論作為源阻抗還是負(fù)載,都極大的改善了濾波器的低頻濾波效能,一定程度上彌補(bǔ)了無源濾波器低頻濾波較差的缺點(diǎn),尤其是作為源阻抗使得濾波器整體濾波性能有了提高。本文引用地址:http://www.104case.com/article/187856.htm

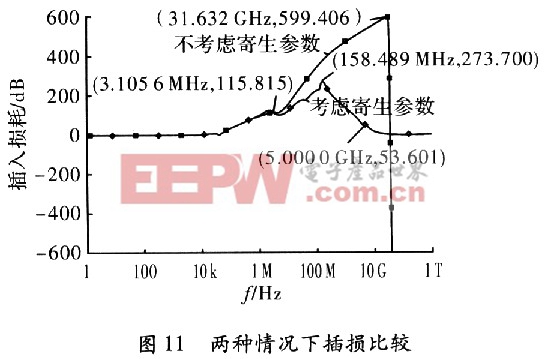

2.4 寄生參數(shù)對濾波器插損影響

理想的EMI濾波器元器件均采用純電容純電感并沒有考慮其高頻寄生參數(shù),而實(shí)際使用的集總參數(shù)元件存在高頻寄生參數(shù),這里給出兩種情況下濾波器插入損耗曲線對比,假設(shè)負(fù)載為純阻性,如圖11所示。

當(dāng)f>3.1 MHz后,由于寄生參數(shù)的影響,插入損耗曲線偏離理想插損曲線,但整體插損依然很高,如圖11所示。在頻率高達(dá)5 GHz時(shí)依然有53.6 dB的插損,說明濾波器在高頻甚至特高頻頻對噪聲抑制能力。

3 結(jié)束語

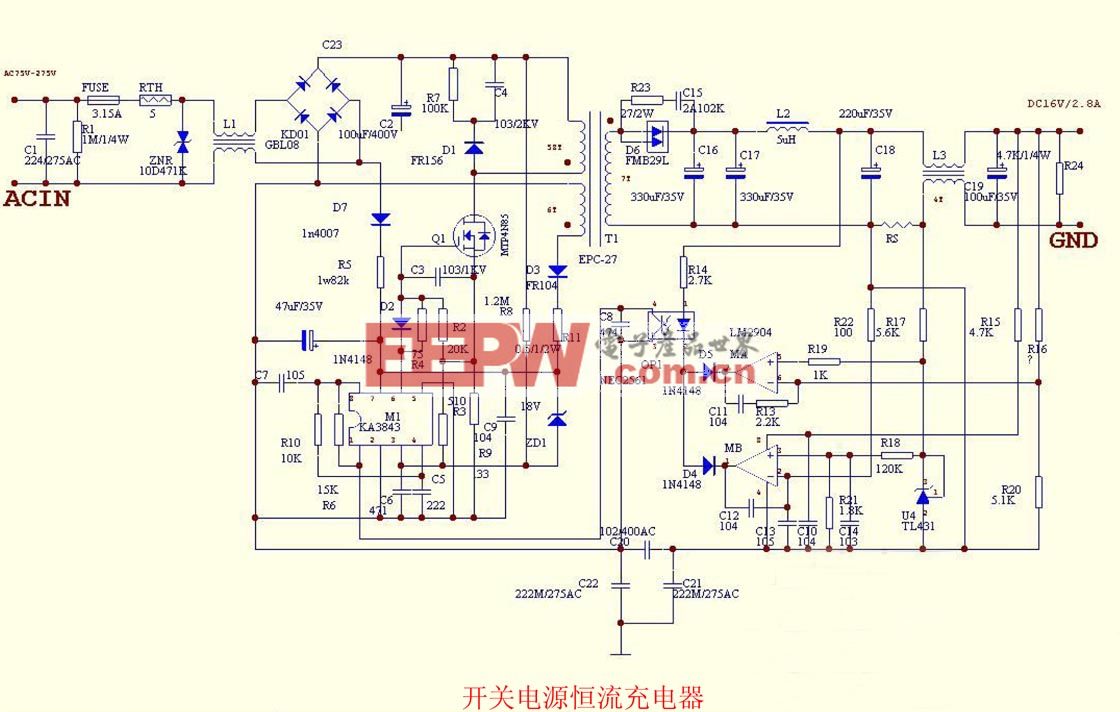

提出的二階無源EMI濾波器,完全濾除了開關(guān)電源輸出端的尖峰干擾,其對開關(guān)電源傳導(dǎo)性共模、差模噪聲干擾體現(xiàn)了較強(qiáng)的抑制作用。同時(shí),分析了源、負(fù)載阻抗特性對濾波器性能的影響,采用TDK元器件模型的濾波器使得理論的仿真更貼近實(shí)際工程應(yīng)用。

評論